# 科研費

# 科学研究費助成事業 研究成果報告書

平成 30 年 6 月 26 日現在

機関番号: 14603 研究種目: 若手研究(B) 研究期間: 2015~2017

課題番号: 15K15960

研究課題名(和文)経年劣化の緩和と監視に基づく高信頼プロセッサの研究

研究課題名(英文)Study on high reliable processor based on mitigation and observation of aging

#### 研究代表者

新谷 道広 (Shintani, Michihiro)

奈良先端科学技術大学院大学・情報科学研究科・助教

研究者番号:80748913

交付決定額(研究期間全体):(直接経費) 2,900,000円

研究成果の概要(和文):半導体製造技術の進歩に伴い,集積回路は我々の生活に欠かせないものになっている一方で,集積回路の構成部品であるMOSトランジスタは経時的に特性が劣化することが知られている.数ある劣化現象の中でも,本研究はバイアス温度安定性(NBTI: Negative bias temperature instability)を対象としており,NBTI劣化のモデル化手法,NBTI依存のパス遅延劣化推定手法および劣化緩和手法の提案を通して,高い安全レベルを確保可能な高信頼プロセッサを実現した.

研究成果の概要(英文): Integrated circuits are now indispensable components of infrastructures to improve quality of our life with advancements of semiconductor technology scaling. On the other hand, the performance of MOS transistors, which is major component of the circuits, is known to severely degrade with time as they are stressed. Among numerous degradation phenomena, this study focuses on bias temperature stability (NBTI: Negative bias temperature instability). By proposing NBTI deterioration modeling method, NBTI-induced path Delay degradation estimation method, and degradation mitigation method, we improve the reliability of large-scale circuits, such as microprocessors.

研究分野:計算機システム

キーワード: トランジスタ MOSFET プロセッサ設計 経年劣化 NBTI タイミング解析 回路シミュレーション

#### 1.研究開始当初の背景

#### 2.研究の目的

トランジスタ性能の経時劣化の要因は 様々あるが、負バイアス温度不安定性(NBTI: Negative bias temperature instability)は、 トランジスタの動作時にストレスがかかり 劣化が進行する劣化現象と、動作していない 時に回復する現象を併せ持つ複雑な劣化現 象であり、劣化後の回路性能予測を困難にしている。

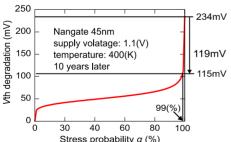

NBTI は ,pMOS トランジスタに負バイア スが印加されている時に遊離した水素イオ ンがゲート酸化膜中に拡散することでトラ ンジスタのしきい値電圧が上昇する現象で あると考えられている.負バイアス印加が終 わると,拡散していた水素が再度結合し,し きい値電圧劣化が回復する.このため,回路 内部における信号線の信号確率が重要とな る.図1に,10年後を想定したしきい値電 圧劣化例を示す.図1の縦軸と横軸は,経年 劣化によるしきい値電圧変化の総量とスト レス確率(信号確率)を示す.ストレス確率 は,MOSFET がストレス状態にある確率を 示す.ストレス確率が 100%の時にしきい値 電圧劣化の進度は非常に大きくなり、逆に 100%からストレス確率を少し下げることで しきい値劣化を大幅に緩和できることが分 かる.

Stress probability a (%) 図 1: 信号確率としきい値電圧劣化の関係

本研究では、ストレス確率を低減することで NBTI による劣化を抑制できることに着目し、命令セットアーキテクチャに、ストレス確率を低減する命令を追加する・また、経年劣化オドメータを実装し、高い機能安全レベルの確保を目指す・経年劣化オドメータは、

事前に命令毎の経年劣化をキャラクタライ

ズし,ルックアップテーブル等で回路上に持たせることで実現する.同時に,設計段階の経年劣化キャラクタライズにより,プロセッサアーキテクチャの信頼性を評価可能となる.これらにより,高信頼性プロセッサを実現する.

#### 3.研究の方法

上述の課題を達成するため,以下の3つの 方法により研究を実施した.

# (1) 高速かつ高精度な回路性能劣化の見積 もり手法

集積回路の長期信頼性を確保するためには、NBTIによる経時的な性能を設計段階で見積もる必要がある.上述のように、NBITの劣化は信号の遷移確率に強く依存する.特に大規模回路内のトランジスタ毎の入力信号確率は、回路に対する入力信号に依存して大きく変化する.本研究では、既存のタイミング解析(STA: Static timing analysis)ま法を、NBTIによる劣化を考慮可能となる元にしているため、プロセッサのような大規模回路においても高速かつ SPICE と同程度の精度で見積もりが可能となる.

## (2) 性能劣化の緩和手法

# (3) 劣化見積もりに基づく経年劣化オドメータ

さらに、経年劣化オドメータを組み込み、高い機能安全レベルの確保を目指す、研究の方法(1)により得られた結果および実測を元に、命令ベースの経年劣化オドメータを設計する、具体的には、経年劣化見積もり結果をルックアップテーブルとして搭載し、実行された命令から経年劣化の進行を積算する経年劣化オドメータを検討する、経年劣化の進行を高精度に監視することで、劣化によるフェイルを事前に検知し、システムの予防的な停止あるいは自己修復が可能となる事を狙う、

# 4.研究成果

## (1) 経年劣化を考慮したパス遅延解析

大規模回路の設計において,デバイス劣化の影響を適切に考慮するため,経年劣化を考慮する高速なタイミング解析手法を実現した.提案手法は,既存のSTA 手法を元に拡張しており,大きく下記3つの経年劣化考慮STAを提案した.

経年劣化を考慮した遅延ライブラリ

従来の STA における遅延ライブラリは,入力信号の遅延(Slew)と出力信号における負荷容量(C\_load)を入力とする2次元テーブルであった.提案手法では,信号確率によるしきい値電圧の劣化量をらに追加することで拡張した.タイミング解析において,逐次このテーブルを参いいるがら,高速にパス遅延劣化量を計算する.本手法を商用 RISC プロセッサに適用し,既存のSPICE ツールによる評価と比べて 7%以下の誤差で 4,114 倍の高速化を達成した.

## 機械学習に基づく経年劣化考慮タイミ ング解析

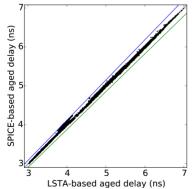

機械学習で小規模回路のタイミング劣化 を学習し,評価対象である大規模回路の 劣化考慮タイミング解析に適用する手法 を提案した.機械学習により経年劣化を 学習することで,多数の経年劣化要因因 子の相関を考慮可能となる.上記 同様 に商用プロセッサに適用したところ, の手法よりも精度よく劣化後のパス遅延 値を推定できた.図2は,提案手法によ る劣化後のパス遅延の推定値とSPICE 回 路シミュレーションによる計算結果の比 較である.図2から,誤差±3%の時の線 を追加しており,推定値がこの範囲内に おさまっていることが分かる.なお,本 研究は,集積回路CADにおける最難関会 議である Design Automation Conference 2017 に採択された.

図 2: 提案手法と SPICE シミュレーション によるパス遅延の推定結果の比較

#### ワークロード依存性の考慮

上記 は.仮定したあるワークロードから一意の信号確率を抽出して計算に用いていた.しかし,実際のプロセッサ稼

# (2) 経年劣化の緩和手法

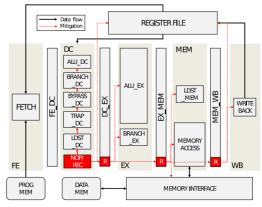

NBTI によるタイミング劣化を効率よく緩 和する手法を提案した,提案手法では,事前 に NBTI の劣化が進む箇所を推定し,オンラ インでこれを緩和する施策を行う.研究成果 (1)から ,ストレス確率により pMOS の劣化量 が推定できるため、事前にプロセッサのワー クロードから付加がかかりやすい箇所を推 定することができる .また ,プロセッサの NOP 動作時に pMOS に負電圧がかかる割合を変化 させる機構を埋め込む.図3は回復機構の一 例であり,命令セットアーキテクチャに回復 のための命令を組み込むことで実現した.類 似の研究は多くあるが,通常動作と回復動作 を独立して行う必要があるが,回復命令は NOP 命令を改良したものであるため,回路動 作時の状態を破壊せず,通常動作と回復動作 を同時に行うことができる.

しかし、この緩和機構は回路オーバーヘッドを伴うため、 遺伝的アルゴリズム、 k-means++アルゴリズム、ニューマンクラスタリング、効率的な枝刈り手法を用いて緩和機構の埋込箇所を選択する手法を開発した.パス遅延は研究成果(1)- のパス遅延劣化の高速計算手法を用いており、商用プロセッサに適当したところ、4%の回路オーバーヘッドで劣化遅延の 44%を緩和できることを示した.

図3: NBTI 考慮プロセッサのアーキテクチャ

(3) 経年劣化モニタのアーキテクチャの検

経年劣化モニタのアーキテクチャの検討:経年劣化を正確にモニタするためには,経年劣化の振る舞いを忠実にモデル化する必要がある.代表的な経年劣化現象であるNBTIには,Reaction-Diffusion モデルとTrapping-Detrapping モデルが知られているが,正当性についてはまだ議論が続いている.本年度は,これらを統合した新たなモデルを提案し,実測から既存の2 モデルより正確であることを示した.

#### 5. 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

#### [雑誌論文](計4件)

Song Bian, Shumpei Morita, Michihiro Shintani, Hiromitsu Awano, Masayuki Hiromoto, and Takashi Sato: "Identification and Application of Invariant Critical Paths under NBTI Degradation," IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences, Vol.E100-A, No.12, pp.2797-2806, Dec. 2017. 杳読有.

DOI:10.1587/transfun.E99.A.1400

Shumpei Morita, Song Bian, Michihiro Shintani, Masayuki Hiromoto, and Takashi Sato: "Utilization of Path-Clustering in Efficient Stress-Control Gate Replacement for NBTI Mitigation," IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences, Vol.E100-A, No.7, pp.1464-1472, Jul. 2017, 査読有.

DOI:10.1587/transfun.E100.A.1464

Michihiro Shintani, Takumi Uezono,

Kazumi Hatayama, Kazuya Masu, and

Takashi Sato: "Path Clustering for

Test Pattern Reduction of

Variation-Aware Adaptive Path Delay

Testing," Journal of Electronic

Testing: Theory and Applications,

Vol.32, Issue 5, pp.601-609, Oct. 2016,

查読有.

DOI:10.1007/s10836-016-5614-0

Song Bian, <u>Michihiro Shintani</u>,

Masayuki Hiromoto, and Takashi Sato:

"Fast Estimation of NBTI-Induced

Delay Degradation Based on Signal

Probability," IEICE Transactions on

Fundamentals of Electronics,

Communications and Computer Sciences,

Vol.E99-A, No.7, pp.1400-1409, Jul.

2016, 査読有.

DOI 10.1587/transfun.E100.A.2797

# [学会発表](計27件)

Mamoru Ishizaka, Michihiro Shintani, and Michiko Inoue: "Area-Efficient Memristor-Crossbar-Based Error Correcting Code Circuit," in Proc. Of Workshop on Security, Reliability, Test, Privacy, Safety and Trust of Future Devices (SURREALIST) (Bremen, Germany), June 2018.

Zuitoku Shin, Shumpei Morita, Song Bian. Michihiro Shintani. Masavuki Hiromoto, and Takashi Sato: Comparative Study of Delav Degradation Caused by NBTI Considering Stress Frequency Dependence, " in Proc. of Workshop on Synthesis And System Integration of Mixed Information technologies(SASIMI) (Matsue, Japan), pp.194-199, Mar. 2018.

Michihiro Shintani, Masayuki Hiromoto, Takashi Sato: "Efficient Parameter-Extraction of SPICE Compact Mode I through Automatic Differentiation, " in Proc. of IEEE International Conference Microelectronic Test Structures (ICMTS) (Austin, TX), pp.35-42, Mar. 2018.

石坂守,新谷道広,井上美智子: "メモリスタニューラルネットワークにおける縮退故障による識別性能への影響",電子情報通信学会総合大会(於東京電機大学),D-10-4,P.58,2018年3月.

Zuitoku Shin, Shumpei Morita, Song Bian, <u>Michihiro Shintani</u>, Masayuki Hiromoto, and Takashi Sato: "A Study on NBTI-induced Delay Degradation Considering Stress Frequency Dependence," in Proc. Of International Symposium on Quality Electronic Design (ISQED) (Santa Clara, CA), pp.251-256, Mar. 2018.

石坂守,新谷道広,井上美智子: "メモリスタ論理による誤り訂正符号回路の設計と評価",電子情報通信学会技術研究報告(ディペンダブルコンピューティング研究会)(於 隠岐の島文化会館),CPSY2017-146,DC2017-102,pp.257-262,2018年3月.

Fakir Sharif Hossain, Tomokazu Yoneda, Michihiro Shintani, Michiko Inoue, and Alex Orailoglu: "A Golden-Free Hardware Trojan Detection Technique Considering Intra-Die Variation,"電子情報通信学会技術研究報告(ディペンダブルコンピューティング研究会)(於機械振興会館), DC2017-84, pp.43-48, 2018年2月.

Shumpei Morita, Song Bian, <u>Michihiro</u> <u>Shintani</u>, Masayuki Hiromoto, and Takashi Sato: "Efficient Worst-case Timing Analysis of Critical-Path Delay under Workload-Dependent Aging Degradation," in Proc. of IEEE/ACM Asia and South Pacific Design Automation Conference (ASP-DAC) (Jeju Island, Korea), pp.631-636, Jan. 2018. Fakir Sharif Hossain, Tomokazu Yoneda, Michihiro Shintani, Michiko Inoue, and Alex Orailoglu:

"Intra-Die-Variation-Aware Side Channel Analysis for Hardware Trojan Detection," in Proc. of IEEE Asian Test Symposium (ATS) (Taipei, Taiwan), pp.48-53, Nov. 2017.

Michihiro Shintani, Masayuki Hiromoto, and Takashi Sato: "Parameter Extraction for MOSFET Current Model Using Backward Propagation of Errors," in Proc. of IEEE/ACM Workshop on Variability Modeling and Characterization (VMC) (Irvine, CA), Nov. 2017.

Song Bian, <u>Michihiro Shintani</u>, Masayuki Hiromoto, and Takashi Sato: "LSTA: Learning-Based Static Timing Analysis for High-Dimensional Correlated On-Chip Variations," in Proc. of ACM/IEEE Design Automation Conference (DAC) (Austin, TX), 73.3, Jun. 2017.

新瑞徳,森田俊平,新谷道広,廣本正之, 佐藤高史: "トランジスタ劣化の永続・ 回復可能成分を考慮したしきい値電圧変 動の時間依存モデル",回路とシステム ワークショップ(於北九州国際会議場), pp.208-213,2017年5月.

Michihiro Shintani, Kazuki Oishi, Rui Zhou, Masayuki Hiromoto, and Takashi Sato: "Device Identification from Mixture of Measurable Characteristics," in Proc. of IEEE Applied Power Electronics Conference and Exposition (APEC) (Tampa, FL), pp.1001-1006, Mar. 2017.

Shumpei Morita, Song Bian, Michihiro Shintani, Masayuki Hiromoto, and Takashi Sato: "Comparative Study of Path Selection and Objective Function in Replacing NBTI Mitigation Logic," in Proc. of International Symposium on Quality Electronic Design (ISQED) (Santa Clara, CA), pp.426-431, Mar. 2017.

Song Bian, <u>Michihiro Shintani</u>, Zheng Wang, Masayuki Hiromoto, Anupam Chattopadhyay, and Takashi Sato: "Runtime NBTI Mitigation for Processor Lifespan Extension via Selective Node Control," in Proc. of

IEEE Asian Test Symposium (ATS) (Hiroshima, Japan), pp.234-239, Nov. 2016

Shumpei Morita, Song Bian, Michihiro Shintani, Masayuki Hiromoto, and Takashi Sato: "Representative Path Approach for Time-Efficient NBTI Mitigation Logic Replacement," in Proc. of IEEE/ACM Workshop on Variability Modeling and Characterization (VMC) (Austin, TX), Nov. 2016.

Michihiro Shintani, Rui Zhou, Kazuki Oishi, Masayuki Hiromoto, and Takashi Sato: "Unique Device Identification Framework for Power MOSFETs Using Inherent Device Variation," in Proc. of IEEE/ACM Workshop on Variability Modeling and Characterization (VMC) (Austin, TX), Nov. 2016.

Shumpei Morita, Song Bian, Michihiro Shintani, Masayuki Hiromoto, and Takashi Sato: "Path Grouping Approach for Efficient Candidate Selection of Replacing NBTI Mitigation Logic, " in Proc. of Workshop on Synthesis And Integration of System Mixed Information technologies (SASIMI) (Kyoto, Japan), pp.225-230, Oct. 2016. 忻瑞徳, 森田俊平, <u>新谷道広</u>, 廣本正之, 佐藤高史: "NBTI によるしきい値電圧変 動のストレス確率依存性の評価",電子情 報通信学会ソサイエティ大会(於 北海道 大学), A-6-2, p.65, 2016年9月.

辺松,新谷道広,廣本正之,佐藤高史: "機械学習による経年劣化タイミング解 析手法",情報処理学会 DA シンポジウム(於 石川県加賀市山代温泉 ゆのくに 天祥),pp.44-49,2016 年9月.

- 21 辺松,新谷道広,森田俊平,粟野浩光, 廣本正之,佐藤高史:"信号確率伝播に基 づくプロセッサのための NBTI 起因最大 遅延パスの抽出",回路とシステムワーク ショップ (於 北九州国際会議 場),pp.30-35,2016年5月.

- 22 森田俊平, 辺松, 新谷道広, 廣本正之, 佐藤高史: "代表パス抽出による劣化緩 和セル置換箇所の高速な選択手法", 回 路とシステムワークショップ(於 北九州 国際会議場), pp.36-41, 2016 年 5 月.

- 23 Song Bian, <u>Michihiro Shintani</u>, Shumpei Morita, Hiromitsu Awano, Masayuki Hiromoto, and Takashi Sato: "Workload-Aware Worst Path Analysis of Processor-Scale NBTI Degradation," in Proc. of ACM Great Lakes Symposium on VLSI (GLSVLSI) (Boston, Massachusetts), pp.203-208, May. 2016.

- 24 Song Bian, <u>Michihiro Shintani</u>, Zheng Wang, Masayuki Hiromoto, Anupam Chattopadhyay, and Takashi Sato:

- "Mitigation of NBTI-Induced Timing Degradation in Processor," in Proc. of ACM International Workshop on Timing Issues in the Specification and Synthesis of Digital Systems (TAU) (Santa Rosa, CA), pp.21-27, Mar. 2016.

- Song Bian, Michihiro Shintani,

Masayuki Hiromoto, and Takashi Sato:

"Nonlinear Delay-Table Approach for

Full-Chip NBTI Degradation

Prediction," in Proc. Of International

Symposium on Quality Electronic Design

(ISQED) (Santa Clara, CA), pp.307-312,

Mar. 2016.

- 26 森田俊平,辺松,新谷道広,廣本正之, 佐藤 高史: "プロセッサの NBTI 劣化緩 和法における劣化抑止制御回路の置換箇 所削減に関する一検討",電子情報通信学 会ソサイエティ大会(於東北大学川内キャンパス), A-3-10, p.55, 2015年9月.

- 27 Song Bian, <u>Michihiro Shintani</u>, Masayuki Hiromoto, and Takashi Sato: "Fast Estimation on NBTI-Induced Delay Degradation Based on Signal Probability",情報処理学会 DA シンポ ジウム (於 石川県加賀市山代温泉 ゆの くに天祥), pp.181-186, Aug. 2015.

[図書](計0件)

# 〔産業財産権〕

出願状況(計0件)

名称: 発明者: 権利者: 種類: 番号:

出願年月日: 国内外の別:

取得状況(計件)

名称: 発明者: 権利者: 種類: 番号:

取得年月日: 国内外の別:

〔その他〕 ホームページ等

http://dslab.naist.jp/

#### 6.研究組織

(1)研究代表者

新谷 道広 (SHINTANI, Michihiro) 奈良先端科学技術大学院大学・情報科学研

| 究科・助教<br>研究者番号:80748913 |   |

|-------------------------|---|

| (2)研究分担者                | ) |

| 研究者番号:                  |   |

| (3)連携研究者                | ) |

| 研究者番号:                  |   |

(

)

(4)研究協力者