# 原子層堆積法による高機能酸化物半導体を 用いた薄膜トランジスタの低温形成と その評価

川村 悠実

2013年3月

奈良先端科学技術大学院大学 物質創成科学研究科

# 目次

| 第1草 汿論                             | 1  |

|------------------------------------|----|

| 1.1 序論                             | 1  |

| 1.2 薄膜トランジスタ(TFT)                  | 2  |

| 1.2.1 ディスプレイ駆動方式                   | 2  |

| 1.2.2 薄膜トランジスタ                     | 4  |

| 1.3 酸化物半導体                         | 5  |

| 1.3.1 透明酸化物材料                      | 5  |

| 1.3.2 酸化亜鉛(ZnO)系酸化物半導体             | 6  |

| 1.4 原子層堆積(ALD)法                    | 7  |

| 1.4.1 原子層堆積(ALD)法の原理               | 7  |

| 1.4.2 プラズマ ALD 法                   | 9  |

| 1.5 背景と目的                          | 10 |

| 1.6 概要                             | 11 |

| 参考文献                               | 13 |

| 第2章 ALD 法による ZnO 薄膜の形成および評価        | 16 |

| 2.1 緒言                             | 16 |

| 2.2 TFT 特性評価方法                     | 17 |

| 2.2.1 電界効果移動度(μ <sub>FE</sub> )    | 17 |

| 2.2.2 閾値電圧(V <sub>th</sub> )       | 18 |

| 2.2.3 サブスレッショルドスイング(S 値)           | 19 |

| 2.3 ALD による ZnO 薄膜の酸化剤による TFT 特性比較 | 20 |

| 2.3.1 ALD による ZnO 薄膜の形成            | 20 |

| 2.3.2 ZnO TFT 作製プロセス               | 21 |

| 2.3.3 ホール効果測定                      | 22 |

| 2.3.4 ZnO TFT 伝達特性                 |    |

| 2.3.5 X 線光電子分光による ZnO 膜の組成評価       | 24 |

| 2.4 ZnO TFT 特性における熱処理の効果           | 27 |

| 2.4.1 熱処理による ZnO TFT 伝達特性の変化       | 27 |

| 2.4.2 電気ストレスに対する信頼性評価              | 29 |

| 2.4.3 X 線回折による結晶性評価                |    |

| 2.4.4 ZnO 膜組成評価                    | 34 |

| 2.5 プラズマ印加時間による ZnO TFT 特性の変化      | 36 |

| 2.5.1    | ZnO TFT 伝達特性                        | 36 |

|----------|-------------------------------------|----|

| 2.5.2    | ZnO 薄膜特性                            | 37 |

| 2.6 PA   | -ALD による ZnO TFT 特性における堆積温度依存性      | 40 |

| 2.6.1    | PA-ALD による ZnO TFT 伝達特性             | 40 |

| 2.6.2    | X 線回折による ZnO 膜の結晶性評価                | 41 |

| 2.6.3    | 二次イオン質量分析 (SIMS) による ZnO 膜の組成評価     | 41 |

| 2.6.4    | 可視光領域における透過率測定                      | 43 |

| 2.7 ラ    | ジカル源による ZnO TFT の高性能化               | 43 |

| 2.7.1    | 水プラズマ ALD による ZnO 薄膜の形成             | 43 |

| 2.7.2    | 水プラズマ ALD による ZnO TFT 特性            | 44 |

| 2.7.3    | 二次イオン質量分析による組成評価                    | 45 |

| 2.7.4    | X 線回折による ZnO 膜の結晶性評価                | 46 |

| 2.7.5    | AFM による ZnO 膜の表面形状評価                | 48 |

| 2.8 結    | 言                                   | 49 |

| 参考文献     | <b>状</b>                            | 51 |

| 第 3 章 Zn | O TFT における ALD による絶縁膜の効果            | 53 |

| 3.1 緒言   |                                     | 53 |

| 3.2 AL   | .D 法による絶縁膜の形成および ZnO TFT 特性への効果     | 54 |

| 3.2.1    | ALD 法による絶縁膜の形成                      | 54 |

| 3.2.2    | ALD による絶縁膜の特性評価                     | 55 |

| 3.2.3    | ALD によるゲート絶縁膜を用いた ZnO TFT 特性        | 56 |

| 3.3 AI   | D によるゲート絶縁膜を用いた低温プロセス ZnO TFT の特性向上 | 58 |

| 3.3.1    | ALD による ZnO TFT 低温作製                | 58 |

| 3.3.2    | ALD による ZnO TFT の電気的ストレス下における信頼性評価  | 59 |

| 3.3.3    | SIMS による深さ方向の組成測定                   | 62 |

| 3.3.4    | ALD による酸化亜鉛薄膜の高機能化に向けた検討            | 64 |

| 3.4 AL   | D による低温プロセス ZnO TFT へのパッシベーション膜の効果  | 66 |

| 3.4.1    | ZnO TFT 上パッシベーション膜の形成               | 66 |

| 3.4.2    | ZnO TFT 特性へのパッシベーション膜の効果            | 67 |

| 3.4.3    | PA-ALD パッシベーション膜による ZnO TFT の信頼性の改善 | 69 |

| 3.5 PA   | -ALD による高性能フレキシブル ZnO TFT の作製       | 71 |

| 3.5.1    | PA-ALD による高性能 ZnO TFT の低温作製         | 71 |

| 3.5.2    | フレキシブル基板上 ZnO TFT 作製プロセス            | 72 |

| 3.5.3    | フレキシブル ZnO TFT 特性                   | 72 |

| 3.5.4 フレキシブル ZnO TFT の信頼性評価               | 73  |

|-------------------------------------------|-----|

| 3.6 結言                                    | 75  |

| 参考文献                                      | 77  |

| 第4章 非晶質 In-Ga-Zn-O TFT 特性における ALD 絶縁膜の効果  | 79  |

| 4.1 諸言                                    | 79  |

| 4.2 In-Ga-Zn-O TFT の作製プロセス                | 79  |

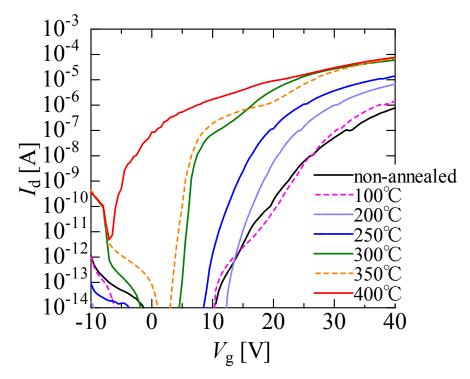

| 4.3 a-IGZO TFT 特性における熱処理の効果               | 80  |

| 4.3.1 TFT 作製後の熱処理による特性の変化                 | 80  |

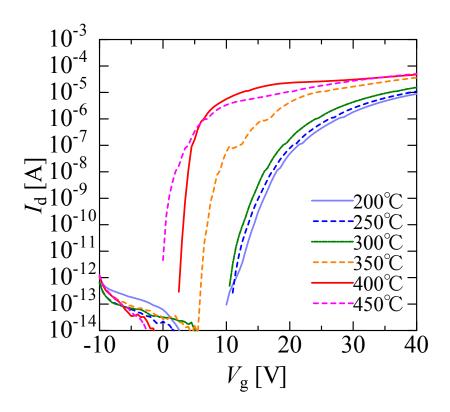

| 4.3.2 TFT 作製前の熱処理による特性の変化                 | 81  |

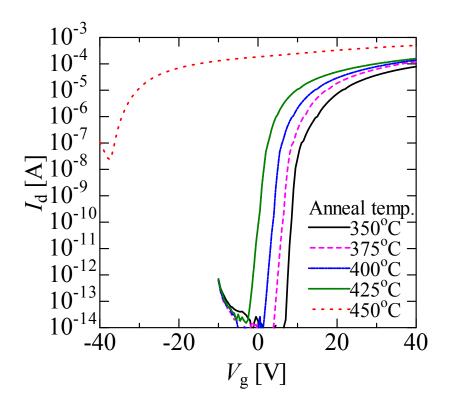

| 4.4 a-IGZO TFT における ALD 絶縁膜の効果            | 83  |

| 4.4.1 a-IGZO TFT における ALD によるパッシベーション膜の効果 | 83  |

| 4.4.2 a-IGZO TFT における ALD によるゲート絶縁膜の効果    | 85  |

| 4.5 結言                                    | 88  |

| 参考文献                                      | 89  |

| 第5章 総括と展望                                 | 90  |

| 5.1 本研究の総括                                | 90  |

| 5.2 今後の展望                                 | 92  |

| 研究業績                                      | 94  |

| I. 投稿論文                                   | 94  |

| II. Proceedings                           | 95  |

| Ⅲ. 学会発表                                   | 95  |

| 国際学会                                      | 95  |

| 国内学会                                      | 97  |

| 謝辞                                        | 100 |

# 第1章 序論

## 1.1 序論

近年のコンピュータ関連技術の発展に伴う高度情報化社会において、マンーマシンインターフェースの一つであるディスプレイの役割はますます大きくなってきている。現在我々の周りには、テレビやパーソナルコンピュータ、スマートフォンに代表されるように、ディスプレイを有した様々な情報端末が存在しており、ディスプレイは人と情報を繋ぐインタフェースとして重要な役割を担っている。さらには、いつでも・どこでも・誰でもこれらの恩恵を受けることができるユビキタスネットワーク社会の実現が迫っており、ディスプレイの果たす役割はさらに重要なものになる。

液晶ディスプレイ(LCD: Liquid Crystal Display)は、過去に主流であったブ ラウン管ディスプレイと比較して薄型、軽量、低消費電力を特徴としたディスプレイ であり、環境保全・省エネルギーの観点よりその重要性が急速に増し、現在はすでに 主流となっている技術である。安全かつ環境負荷の少ない社会を実現するためには、 ディスプレイは今後も形を変え、次世代へ発展していくと考えられる。この革新の一 つとして、透明で湾曲することができるフレキシブルなディスプレイやコンピュータ の開発が進められている。これが実現されれば、ユビキタスネットワーク社会に大き く貢献することになるであろうと考えられる。近未来予想図として映像作品に用いら れてきた未だ実現されていないこの次世代素子は、これまで映画の中だけの世界であ ったものを現実のものとし、人々の生活を豊かにするであろうことは想像に難くない。 このようなディスプレイを構成する重要な素子に薄膜トランジスタ(TFT: Thin Film Transistor)がある。これは、我々の日々の生活を支えるディスプレイに既に広く使用 されている素子であり、次世代ディスプレイにとっても無くてはならない素子となる。 TFT の機能は画素の表示・非表示を切り替えるスイッチングを行うことであり、そこ に使用されている半導体薄膜により、その性能は大きく左右される。TFT を透明でフ レキシブルなディスプレイに適用するためには、半導体薄膜もその性能を維持しなが ら透明、フレキシブルという条件を満たさなければならない。しかしながら、現在半 導体薄膜材料として、シリコンが一般的に使用されており、要求されるこれらの条件 を満たすことは困難である。このような背景により、近年この条件を満たし得る材料 として、金属酸化物の半導体特性が注目され始めた。酸化物半導体は3 eV 以上のバ ンドギャップを持つことから、可視光に対して透明な材料である。また、酸化物半導 体薄膜は室温で成膜することが可能であることから、応用に十分なデバイス特性を備 えた、次世代ディスプレイの構成材料として最も適していると位置づけられる。

本研究は、次世代ディスプレイの実現に向け、高性能金属酸化物半導体薄膜の形成と、その実用化を目的としている。

## 1.2 薄膜トランジスタ (TFT)

#### 1.2.1 ディスプレイ駆動方式

ディスプレイの駆動方式には、パッシブマトリクス (PM: Passive Matrix )型駆動方式と、アクティブマトリクス (AM: Active Matrix )型駆動方式があり、PM型駆動方式は TFT がなく、走査配線と信号配線とで画素を駆動する。しかし、この方式では隣接する画素にかかる電圧の影響を受ける、前画像の残像があるなどの問題がある。そこで、各画素にスイッチングトランジスタを入れることにより、隣接する画素信号の影響を受けないようにした AM型駆動方式が、大画面化するディスプレイに用いられるようになった。ディスプレイの薄型化・モバイル化に伴い、トランジスタにも薄型化・微細化が要求され、TFT が使用されるようになった。<sup>1)</sup>

AM 型ディスプレイは、1971 年 RCA 社の Lechner らにより提案された。<sup>2)</sup> その後、TFT 駆動の液晶ディスプレイ(LCD: Liquide crystal display)の開発が世界中で行われ、現在ではテレビやパーソナルコンピュータをはじめとするデジタル家電など多くの機器に搭載されている。今後も新しいディスプレイの駆動にはその性能に対応した TFT が必要になると考えられる. 次世代ディスプレイとしてはオフィスや電車の窓がすべてディスプレイとして使用できる透明ディスプレイ <sup>3,4)</sup>、巻き取ってコンパクトに持ち歩くことができるフレキシブルディスプレイ <sup>5,6)</sup>、衣服やメガネ、時計などにディスプレイ表示を行うウェアラブルディスプレイなどが提案されている。

現在、透明でフレキシブルな次世代ディスプレイやガラス上コンピュータの実現による、ユビキタスネットワーク社会を目指した研究が盛んに行われている。フレキシブルディスプレイは、薄くて曲げることができるなどの特徴をもつ新しいディスプレイであり、医療やレスキュー現場への応用や、環境負荷の低減等の環境面への配慮から、現在このフレキシブルディスプレイの開発が求められている。図 1-1 は、世界で初めて我が国で発売された、酸化亜鉛 (ZnO) 系 TFT を画素駆動素子とした有機 EL ディスプレイを搭載したスマートフォンである。また、これまでに発表された透明ディスプレイ、フレキシブルディスプレイなど次世代ディスプレイの例を、図 1-2 に示す。ユビキタス社会に適応した次世代ディスプレイ用 TFT では、その構成材料に「透明」であり「フレキシブル基板上への作製が可能」といった条件が求められる。

図 1-1 酸化亜鉛系 TFT 駆動有機 EL ディスプレイ搭載スマートフォン(Sharp, 2012) $^{7)}$

図 1-2 次世代ディスプレイ 8-13)

## 1.2.2 薄膜トランジスタ

トランジスタは、バイポーラトランジスタと電界効果トランジスタ(FET: Field Effect Transistor) に分類される。薄膜トランジスタは、半導体材料を用いて作製される FET の一種である。電界効果トランジスタは、1930年ドイツの Leipzig 大学の J. Lilienfeld が、固体電子装置の特許をカナダに提出したことから始まる。<sup>14)</sup> その後、1947年に点接触型トランジスタが、アメリカ Bell 研究所の J. Bardeen, W. H. Brattain によって発明された。翌年には同研究所の W. B. Shockley Jr. により、バイポーラトランジスタの理論が証明された。その後も Bell 研究所ではトランジスタの研究が盛んに行われ、1960年にシリコンの金属/酸化物/半導体(MOS: Metal/Oxide/Semiconductor)トランジスタが発明された。

世界初の TFT は、1962 年に硫化カドミウム(CdS) を用いて試作された。 $^{15)}$  そ の後、1973年にTFTをアドレス素子として用いた AM 型無機 EL ディスプレイの試 作が報告されている。<sup>16)</sup> このように、TFT の研究はⅡ-VI族化合物カルコゲナイド半 導体から始まった。当時光導電デバイスとして盛んに研究されていたこれらの材料は、 真空蒸着を用いた薄膜が容易に形成でき、5~50 cm<sup>2</sup>/Vs という高いホール移動度を持 つが、一方で、膜質制御や界面欠陥制御が困難であり、n型が作製できない、毒性材 料であるなど様々な課題を抱えていた。1975年にイギリス Dundee 大学の Spear らが 価電子制御可能な水素化非晶質シリコン(a-Si:H)薄膜を提案し、17,18 1979年にはこ れを用いた TFT を報告した。19) これは大変重要な発明であり、現在のディスプレイ 駆動 TFT の主流は Si 系材料となっている。Si を用いた TFT には、a-Si:H<sup>20,21)</sup>、微結 晶 Si (μc-Si )<sup>22)</sup> 、低温ポリシリコン(LTPS: Low temperature poly crystalline silicon)<sup>23,24)</sup> 、高温ポリシリコン(HTPS: High temperature poly crystalline silicon)<sup>25)</sup> 、 単結晶 Si がある。<sup>26)</sup> 次世代ディスプレイに対応する TFT の試作においても、これら a-Si:H や LTPS を用いて開発が進められてきた。<sup>27)</sup> LTPS-TFT は a-Si:H TFT より二桁 高い  $100 \text{ cm}^2/\text{Vs}$  という高い電界効果移動度を持つ高性能な TFT である。 $^{28)}$  しかし、 チャネルに結晶粒界を含むことで TFT 特性のばらつきが生じるなどの問題を抱えて いる。a-Si:H を用いた場合では、TFT 特性の不均一性を抑えることが可能であるが、 a-Si:H TFT の電界効果移動度はLTPS-TFT の 1/100 程度であり、次世代の高精彩ディ スプレイ駆動に要求される特性を得ることは困難である。従って、プラスチック基板 などのフレキシブル基板上に、低価格で大面積に形成できる十分な性能を持った素子 の開発が望まれる。このような背景から、低温形成が可能である有機 TFT や、室温で 形成された酸化物半導体を用いた TFT も登場し<sup>29-31)</sup>、世界初の TFT に用いられた化 合物半導体が再び注目されている。

近年実用化が始まった OLED は電流駆動素子であり、画面のピーク輝度の向

上には、駆動 TFT の駆動電流( $I_{\rm d}$ )の向上,すなわち電界効果移動度の向上が必要である。さらに、大画面化に伴い同一輝度の実現に必要とされる  $I_{\rm d}$ が増大することから、画素駆動用 TFT の高移動度化が求められる。次世代ディスプレイにおいては、約 1 億個の TFT が必要とされるため、高移動度の TFT を用いることにより TFT のチャネル幅を小さくできるという利点もある。また、OLED では、画素間の駆動 TFT の  $I_{\rm d}$  のばらつきが輝度のばらつきとして視認されるため、TFT には特性の均一性が強く要求される。

そこで、次世代ディスプレイの画素駆動素子として要求される「透明」「フレキシブル」「高移動度」の条件を満たす半導体材料として、現在は酸化物半導体が最有力候補とされている。

## 1.3 酸化物半導体

#### 1.3.1 透明酸化物材料

透明性とは可視光透過性を指しており、透明な材料とは 3.3eV 以上のエネルギーギャップを有する材料である。現在半導体材料として一般的に使用されている Si(1.1eV)や GaAs(1.42eV)と比較して、透明材料はエネルギーギャップが大きく、ワイドギャップ材料と呼ばれる。ワイドギャップ材料には、酸化亜鉛(ZnO)に代表される酸化物半導体が挙げられる。

酸化物材料は、酸化シリコンに代表される絶縁材料から、透明導電膜に代表される導電材料まで、広範囲な導電率を示す。透明導電膜としての透明酸化物材料は、1947年頃より透明導電性材料として研究され始めた。1954年、R.E. Aitchison により酸化インジウム  $(In_2O_3)$  が高い導電性を示すという報告がされた後  $^{32)}$ 、その電気的・物理的特性が多くの研究者により明らかにされ、低抵抗率で透明度の高い薄膜が形成できるようになった。その結果、現在タッチパネル用透明導電膜などに一般的に使用されている、酸化インジウムに 5-10%程度のスズをドープした Indium-Tin-Oxide (ITO)等、透明導電膜として広く利用されるようになった。

代表的な透明酸化物材料としては、 $In_2O_3$ 、 $SnO_2$ 、ZnO などが挙げられる。中でも、ITO は透明導電膜材料として広く実用化されている。しかしながら、近年のIn の枯渇化や、それに伴う価格の急騰により、VアメタルであるIn の代替技術が検討され始めた。ITO の代替材料として、近年、酸化亜鉛が国内外から注目されている。亜鉛鉱はインジウムと異なり、世界中に広く分布しているため、コストや供給量など生産面において優れているほか、可視光領域ではITO よりも高い透過率を示すなど、特性面においても優れた特性を有している。

#### 1.3.2 酸化亜鉛(ZnO)系酸化物半導体

現在、高速応答の液晶や、有機 EL ディスプレイといった次世代ディスプレイ内のスイッチング素子として、チャネル層にアモルファスシリコンや多結晶シリコン (poly-Si) を使用した TFT が広く用いられている。しかしながら、次世代放送規格であるスーパーハイビジョンに対応するディスプレイにおいては、10cm²/Vs 以上の電界効果移動度が要求されると試算されており、従来の a-Si:H TFT(~0.5cm²/Vs)では不可能となっている。 33) さらに、TFT 作製工程において高温プロセスが必要、広い面での形成が困難であり、また、透明な素子の作製にあたり Si 材料は適さない等といった、今後の新しいディスプレイへの応用に関しての問題がある。従って、プラスチック基板などのフレキシブル基板上に、低価格で大面積に形成できる十分な性能を持った新しい材料による素子の開発が必要となる。そこで、近年、ZnO 等の酸化物半導体が、Si 系材料に代わる新しい材料として注目され、世界中の研究機関で研究されている。

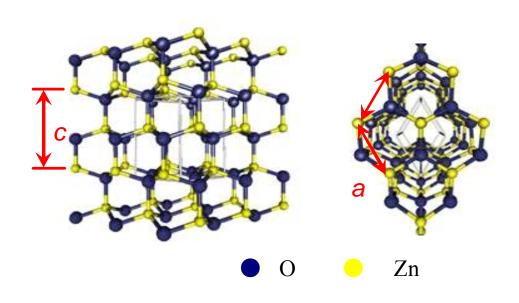

ZnO は、図 1-3 に示すようにウルツ鉱型構造で六方晶の結晶を持ち、その比抵抗は、 $Al^{3+}$ や  $In^{3+}$ ドープ時には  $10^4$   $\Omega$  cm、 $Li^+$ ドープ時には  $10^{10}$   $\Omega$  cm と、14 桁も変化することから、導電膜としても誘電膜としても開発が進められている興味深い材料である。また、室温で 3 eV 以上のバンドギャップを有するワイドバンドギャップ材料である。従って、電子デバイス用材料として、特に透明性や高耐圧を必要とされるものへの応用に適している。このような応用に対しては、窒化ガリウム(GaN)系材料やシリコンカーバイド(SiC)を利用したデバイスの開発が進んでいる。しかし、GaN や SiC は 1000  $^{\circ}$   $^{\circ}$

以上のような特徴から、ZnO はフレキシブルディスプレイや透明ディスプレイなど、次世代ディスプレイのスイッチング素子を構成する材料として、非常に適した特性を持つ物質であると考えられる。ZnO のデバイスへの応用を拡大するためには、電界効果デバイスへの応用が不可欠である。ZnO 電界効果デバイスの研究は、G.F.Boessen らにより 1968 年に初めて ZnO FET に関する報告 <sup>34)</sup> がされたが、その後 2003 年に ZnO を使用した TFT の報告 <sup>35-37)</sup> がされるまで、35 年間という長期にわた

る空白期間が存在する。ZnO に代表される酸化物半導体では、酸素欠損や格子間亜鉛といった欠陥により、不純物をドーピングしない状態においても成膜条件や熱処理により、その導電率やキャリア濃度が大幅に変化することが、デバイスへの応用において壁となってきた。しかしながら、その優れた特徴から、ZnO 電界効果デバイスである ZnO TFT の開発が、近年世界的に活発となっている。

図 1-3. 酸化亜鉛結晶構造 38)

## 1.4 原子層堆積(ALD)法

#### 1.4.1 原子層堆積 (ALD) 法の原理

原子層堆積(ALD: Atomic Layer Deposition)法とは、フィンランドの Sunatola らによりその基本概念が考案された手法である。基板表面に原料ガスを単分子吸着させ、異なる前駆体を交互に供給することによりこの吸着分子を化学反応により基板上で固層へと変えていく成膜方法である。<sup>39)</sup>供給された前駆体は、表面反応により基板表面へと吸着し、すべてのサイトが飽和すると反応は自己停止する。この1原子層ごとの堆積と自己停止型表面反応により、広い面積に対し均質、均一で精密な膜厚制御の成膜が可能となる。有機 EL の硫化亜鉛薄膜や化合物半導体であるガリウムヒ素薄膜の形成手法として発展してきた <sup>39-42)</sup>が、この技術が考案された当時は、薄膜のエピタキシャル成長の手法として用いられていたことから、ALE (Atomic Layer Epitaxy) <sup>43)</sup>と称されていた。しかし近年、非晶質膜や多結晶膜の形成にも用いられる

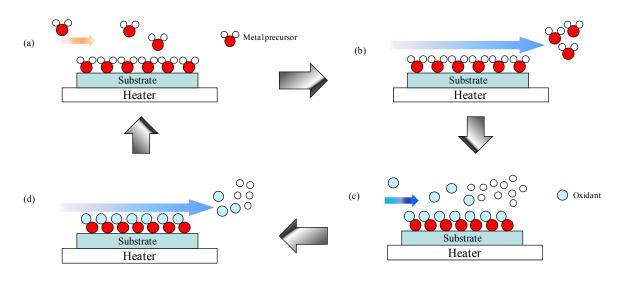

ようになり、ALD 法と呼ばれるようになった。原子層レベルでの膜厚制御、大面積に均質な成膜が可能である本技術は、今日のLSI の高性能化に伴い大きな注目を集めており、ALD 法により形成された  $HfO_2/Al_2O_3$  膜が DRAM キャパシタ膜として量産されるに至っている。  $^{44-47)}$  さらに、一般的な平行平板型プラズマ化学気相成長法 (PE-CVD) などと比較して低温でも緻密な膜が得られることが分かっている。  $^{48)}$  図 1-4 (a)~(d) に、本研究で用いた ZnO 薄膜の成膜サイクルを例に挙げ、ALD 法による基本的な成膜サイクルを示す。

- (a)ヒータ上に基板を配置したチャンバー内に、金属材料を導入する。

- (b)チャンバー内の余剰分子を不活性ガスによりパージする。

- (c)酸化剤を投入し、金属原料と反応し酸化物を形成する。

- (d)チャンバー内の余剰分子を不活性ガスによりパージする。

この(a)~(d)のサイクルを繰り返すことにより成膜を行う。

近年、ディスプレイなどの製造において、その高品質化のために、絶縁膜、保護膜、 封止膜などに ALD 法の適用が検討され始めている。例として、有機 EL ディスプレイ は、大気中にある水分および酸素によって劣化する。この水分および酸素の透過防止 保護膜として、ALD により堆積された Al<sub>2</sub>O<sub>3</sub> 膜が期待されている。

図 1-4 ALD 成膜サイクル

#### 1.4.2 プラズマ ALD 法

ALDプロセスはその反応の活性化手段の面から、基板を加熱する熱エネルギーによる反応を用いた従来の熱 ALD 法と、反応の活性化にプラズマを印加するプラズマ ALD 法の二つに大別することができる。プラズマ ALD 法は、プラズマにより反応を促進する手法であり、成膜速度、プロセスの低温化等を向上させるという報告があり、近年注目され始めている。一方で、熱 ALD 法は装置の簡略化、低コスト化が可能となる。

プラズマ ALD 法では、そのプラズマの適用方法により、金属原料と酸化剤の反応の際に直接プラズマを印加するダイレクトプラズマ方式と、反応を行うリアクタ外でプラズマを使用し活性化された反応基を導入するリモートプラズマ方式に大別される。さらに、そのプラズマの導入方式により、Direct-plasma, Plasma-enhanced, Remote-plasma, Plasma-assisted ALD 等が挙げられるが、これらを総称しプラズマ ALD (Plasma-ALD) とされ、プラズマ ALD に関する研究の報告が、近年増加する傾向にある。

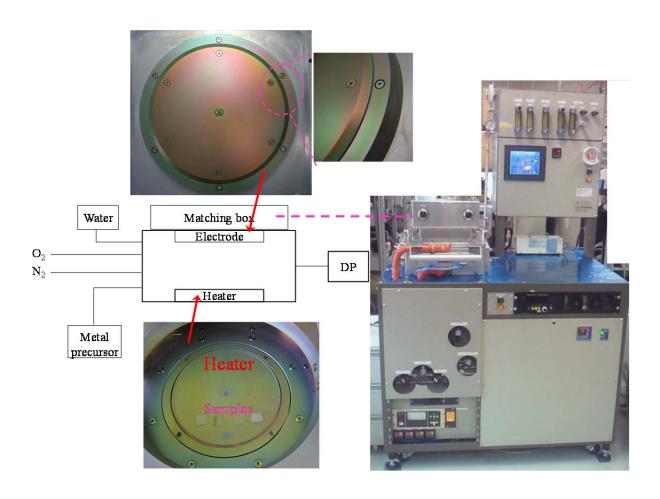

本研究では、酸化剤にプラズマを印加し活性化したプラズマ酸素を酸化剤として使用する、プラズマ援用(PA: Plasma Assisted)-ALD 法を用い、高品質な薄膜の低温形成を目指した。本研究で使用した ALD 成膜装置の外観画像および概略図を、図1-5 に示す。

図 1-5 ALD 装置概略図(MES-AFTY, AFTEX 600)

## 1.5 背景と目的

先に述べたように、ZnO は古くから研究され生活に用いられてきた材料である。しかしながら、半導体デバイスへの応用が注目され始めたのは比較的最近のことであり、その応用に関して、まだ十分に研究されていない。近年、TFT のチャネル層としての ZnO 膜の応用が、その固有の特性により注目されている。 49-55) ZnO はワイドバンドギャップ (~3.37 eV) であり、また、広い面積に低温での成膜が可能であるため、プラスチックやフレキシブル基板上での形成が可能となる。さらに、ZnO TFT は a-Si:H TFT よりも高い電界効果移動度が得られることが報告されている。しかし、その TFT への応用に関しての信頼性や様々な環境下での安定性は、まだ十分に実証されていない。

ZnO 薄膜の電気的特性および安定性を調べるため、我々は、ALD 法による薄膜の形成に着目した。ALD 法は、原料ガスと酸化剤を交互に供給し 1 原子層ごとに

堆積する手法であり、正確な膜厚制御性、高い膜厚均一性を有し、広い面積への良質な膜の形成が可能であることから、半導体素子製造分野において注目されている手法の一つである。 $^{50}$  また、ALD によって堆積された膜により、デバイスへの応用の際に高い電界効果移動度が得られたという報告がされている。 $^{57-59)}$

本研究の目的とする次世代ディスプレイへの応用においては、情報量の増大 に対応するための高移動度(>10cm $^{2}$ V $^{-1}$ s $^{-1}$ ) や、プラスチックなどのフレキシブル基板 上に形成するための作製プロセスの低温化(~150℃) などが求められる。現在一般的 に用いられている a-Si:H TFT において課題となっている電界効果移動度の不足、およ び、プラスチックなどのフレキシブル基板へのデバイスの作製を困難としている高い プロセス温度などの課題を解決する必要がある。この課題をクリアできる新しいデバ イス材料として注目されている酸化物半導体の中でも、酸化亜鉛は有力な候補とされ ている。しかしながら、酸化亜鉛薄膜は室温での形成は可能であるが、デバイスとし て使用する際にはその特性の向上のため高温のプロセス(>300℃)が必要とされて おり、現状では未だ課題の解決には至っていない。本章2節において、これまでに発 表されてきた次世代ディスプレイの例を示したが、これらのディスプレイではそのほ ぼ全てが ZnO にレアメタルであるインジウムやガリウムを添加した非晶質 In-Ga-Zn-O を用いた TFT を使用している。また、高温プロセスを使用しているため、 フレキシブルディスプレイにおいても高耐熱の特殊な基板の使用が必要となってお り、移動度などの性能においても次世代ディスプレイの実用に向けては多くの課題が 残されている。

そこで、本研究では、大面積に対して高い均一性を有し、低温でも高品質な薄膜の形成が可能である ALD 法の ZnO 膜形成への適用を提案した。次世代ディスプレイの駆動素子への応用を目指し、高い電気的特性を持つ ZnO TFT の、低温での形成を目的とした。そこで、ALD により堆積された ZnO 膜をチャネル層とした TFT を作製し、その電気的特性の評価を行った。

## 1.6 概要

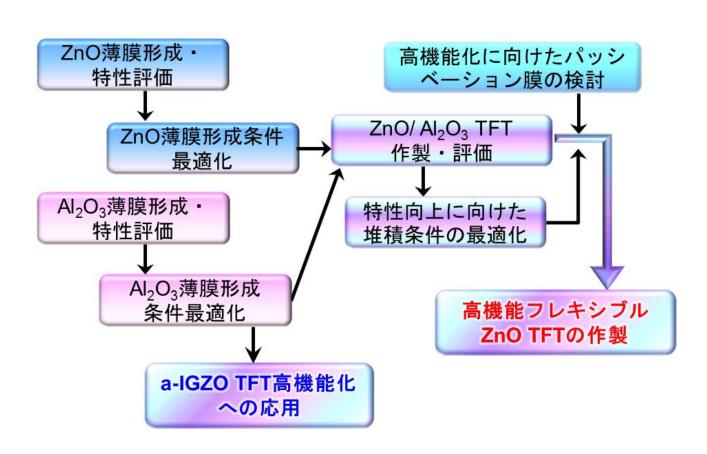

本研究では、次世代ディスプレイの駆動素子として酸化物半導体を用いた TFT の実用化を目的とし、高性能な ZnO TFT の低温での作製を目指した。

第2章では、ALDにより堆積した ZnO 膜を用いて TFT を作製し、プロセスの低温化への可能性を評価した。従来の熱 ALDと本研究で提案するプラズマ ALDで堆積した ZnO 膜を使用し、ZnO 膜の膜特性を比較することにより、ZnO TFT の特性向上に向けた指標の特定を試みた。PA-ALDで形成した ZnO 膜を使用した TFT の、

成膜および TFT 作製後の熱処理に対する特性の変化を調べた。熱処理雰囲気及び温度に対する特性の変化を調べることにより、特性変化の原因を検討した。 さらに、 PA-ALD による ZnO TFT の更なる高性能化に向け、プラズマソースに水を使用した ZnO 膜を形成し、その特性を評価した。

第3章では、ZnO TFT 作製プロセスの低温化に向け PA-ALD によりアルミナ膜を低温形成し、プラズマ印加条件によるアルミナ膜の特性の変化を調べた。このアルミナの特性と ZnO TFT のゲート絶縁膜として使用した際の特性の変化を比較し、ZnO TFT 特性の向上への効果を検討した。さらに、TFT 作製プロセスの低減のため、前章で得られた ALD による絶縁膜の特性を元にゲート絶縁膜も ALD で形成し、高性能 ZnO TFT の低温プロセス化を試みた。

第4章では、ALDにより堆積した薄膜の、酸化物半導体デバイスへの応用として、現在酸化物半導体の中でも非晶質材料として注目されている a-In-Ga-Zn-O を使用した TFT に対する、ALD により形成した絶縁膜の効果を調べた。

図 1-6 本研究の概要

## 参考文献

- <sup>1)</sup> 薄膜材料デバイス研究会編,*薄膜トランジスタ*,株式会社 コロナ社 (2008).

- <sup>2)</sup> B. J. Lechner, F. J. Marlowe, E. O. Nester, and J. Tults: *Proc. IEEE*, **59** (1971) 1566.

- 3) H. –H. Hsieh, T. –T. Tsai, C. –M. Hu, C. –L. Chou, S. –F. Hsu, Y. –C. Wu, C. –S. Chuang,

- L. -H. Chang, and Y. Lin: SID Dig. Tech. Pap., (2011) 714.

- <sup>4)</sup> S. –H. K. Park, S. Yang, H. Oh, C. –S. Hwang, M. Ryu, J. Pi, I. Y. Eom, O. S. Kwon, and E. Park: *IDW Dig. Tech. Pap.*, (2011) 1665.

- S. Nakano, N. Saito, K. Miura, T. Sakano, T. Ueda, K. Sugi, H. Yamaguchi, I. Amemiya, M. Hiramatsu, A. Ishida, K. Kanomaru, and M. Sawada: *IDW Dig. Tech. Pap.*, (2011) 1271.

- 6) J. Chen, J. -W. Shiu, W. -W. Chiu, C. -C. Tsai, and C. -Y. Huang: *SID Dig. Tech. Pap.*, (2011) 107.

- 7) http://www.sharp.co.jp/igzo/, (12/2012).

- 8) http://www.sony.co.jp/SonyInfo/, (01/2010).

- 9) http://www.toshiba.co.jp/about/press/index j.htm, (04/2011).

- <sup>10)</sup> http://www.ceatec.com/2010/ja/, (01/2013).

- 11) http://docomo-exhibition.jp/wj2012/, (12/2012).

- http://techon.nikkeibp.co.jp/fpd/, (12/2012).

- http://www.displaybank.com/jpn/share/index.html, (12/2012).

- <sup>14)</sup> J. E. Lilienfeld: *US Patent.*, 1745175 (1930).

- <sup>15)</sup> P. K. Weimer: *Proc. IRE.*, **50** (1962) 1462.

- <sup>16)</sup> T. P. Brody, J. A. Asaras, and G. D. Dixon: *IEEE Trans. Elec. Dev.*, **ED-20** (1973)995.

- <sup>17)</sup> W. E. Spear and P. G. Le Comber: *Solid State Commun.*, **17** (1975) 1193.

- W. E. Spear and P. G. Le Comber: *Philosophical Magazine*, **33** (1976) 935.

- <sup>19)</sup> P. G. Le Comber, W. E. Spear, and A. Ghaith: *Electron. Lett.*, **15** (1979) 179.

- <sup>20)</sup> K. Takechi, N. Hirano, H. Hayama, and S. Kaneko: *J. Appl. Phys.*, **84** (1998) 3993.

- <sup>21)</sup> C. –C. Chian, J. –Y. Nahm, T. Li, J. Kanickia, and Y. Ukai: *Jpn. J. Appl. Phys.*, **40** (2001) 530.

- E. Takahashi, Y. Nishigami, A. Tomyo, M. Fujiwara, H. Kaki, K. Kubota, T. Hayashi, K. Ogata, A. Ebe, and Y. Setsuhara: *Jpn. J. Appl. Phys.*, **46** (2007) 1280.

- Y. Mishima, M. Takei, N. Matsumoto, T. Uematsu, U. Wakino, T. Kakehi, and M. Okabe: *Appl. Phys. Lett.*, **66** (1995) 31.

- <sup>24)</sup> M. Cao, T. Zhao, K. C. Saraswat, and J. D. Plummer: *IEEE Trans. Elec. Dev.*, **42** (1995) 1134.

- <sup>25)</sup> T. Ohshima. T. Noguchi, and H. Hayashi: *Jpn. J. Appl. Phys.*, **25** (1986) L291.

- N. M. Johnson, D. K. Biegelsen, H. C. Tuan, M. D. Moyer, and L. E. Fennell, *IEEE Elec. Dev. Lett.*, **EDL-3**, (1982) 12.

- <sup>27)</sup> 鵜飼育弘,*a-Si:H TFT-LCD の最新技術,*ED リサーチ社,(2006).

- <sup>28)</sup> 鵜飼育弘, *低温ポリSi TFT-LCD 技術*, ED リサーチ社, (2005).

- <sup>29)</sup> R. L. Hoffman, B. J. Norris, and J. F. Wager: *Appl. Phys. Lett.*, **82** (2003) 733.

- <sup>30)</sup> P. F. Carcia, R. S. McLean, M. H. Reilly, and G. Nunes, Jr: *Appl. Phys. Lett.*, **82** (2003) 1117.

- <sup>31)</sup> E. M. C. Fortunato et al., *Appl. Phys. Lett.*, **85** (2004) 2541.

- <sup>32)</sup> R.E. Aitchison: *J. Appl. Sci.*, **5** (1954) 10.

- Y. Matsueda: *Proc. of the 6<sup>th</sup> International Thin-Film Transistor conference*, (2010) 314.

- <sup>34)</sup> G.F. Boesen, and J. E. Jacobs: *Proc. IEEE*, Nov 2094, (1968).

- J. Nishii, F. M. Hossain, S. Takagi, T. Aita, K. Saikusa, Y. Ohmaki, I. Ohkubo, S. Kishimoto, A. Ohtomo, T. Fukumura, F. Matsukura, Y. Ohno, H. Koinuma, H. Ohno, and M. Kawasaki: *Jpn. J. Appl. Phys.* **42** (2003) L347.

- <sup>36)</sup> S. Masuda, K. Kitamura, Y. Okumura, S. Miyatake, H. Tabata, and T. Kawai: *J. Appl. Phys.*, **93** (2003) 1624.

- <sup>37)</sup> R. L. Hoffman, B. J. Norris, and J. F. Wager: *Appl. Phys. Lett.*, **82** (2003) 733.

- <sup>38)</sup> 八百隆文,*ZnO 系の最新技術と応用*, 株式会社 シーエムシー出版 (2007).

- <sup>39)</sup> T. Suntla and I. Anston: *Finnish Patent* No. 52359, (1974).

- T. Suntla, J. Antson, A. Pakkala and S. Lindfors: *Dig. 1980 SID Int. Symp., San Diego,* 1980 (Society for Information Display, Los Angeles, 1980) 108.

- <sup>41)</sup> J. Nishizawa, H. Abe, and T. Kurabayashi, *J. Electrochem. Soc.*, **132** (1985)1197.

- <sup>42)</sup> 纐纈明伯,高橋直行,関 壽: *応用物理*, **63**(1994)682.

- 43) L. Niinisto: Current Opinion in Solid state & Materials Science, 3(1998) 147.

- O. Sneh, R. B. Clark-Phelps, A. R. Londer gan, J. Winkler, and T. E. Seidel: *Thin Solid Films*, **402** (2002) 248.

- 45) S. Haukka: *Nikkei Microdevices*, **10**(2000)102.

- M. Gutsche, H. Seidl, T. Hecht, S. Kudelka, and U. Schroeder: *Future Fab Intl.* 14(2003).

- <sup>47)</sup> 橋本哲一: Nikkei Microdevices, **5**(2004)49.

- <sup>48)</sup> K. Washio, Y. Mori, N. Miyatake, K. Murata, Y. Sugawara, and Y. Uraoka: *IDW'07* (2007) 549.

- <sup>49)</sup> R. B. M. Cross and M. M. D. Souza: *Appl. Phys. Lett.* **89** (2006) 263513.

- <sup>50)</sup> Ü. Özgür, Ya. I. Alivov, C. Liu, A. Teke, M. A. Reshchikov, S. Doğan, V. Avrutin, S. J.

- Cho, and H. Morkoç: J. Appl. Phys., 98 (2005) 041301.

- <sup>51)</sup> Y. Ohya, T. Niwa, T. Ban, and Y. Takahashi: *Jpn. J. Appl. Phys.*, **40** (2001) 297.

- S. Matsuda, K. Kitamura, Y. Okumura, and S. Miyatake: J. Appl. Phys., 93 (2003) 1624.

- <sup>53)</sup> R. L. Hoffman, B. J. Norris, and J. F. Wager: *Appl. Phys. Lett.*, **82** (2003) 733.

- <sup>54)</sup> P. F. Carcia, R. S. McLearn, M. H. Reilly, and G. Nunes: *Appl. Phys. Lett.*, **82** (2003) 1117.

- E. Fortunato, P. Barquinha, A. Pimentel, A. Goncalves, A. Marques, L. Pereira, and R. Martins: *Thin Solid Films*, **487** (2005) 205.

- <sup>56)</sup> K. Murata, K. Washio, N. Miyatake, Y. Mori, H. Tachibana, Y. Uraoka, and T. Fuyuki: *ECS Trans.*, **11** (2007) No. 7, 31.

- <sup>57)</sup> S. Kwon, S. Bang, S. Lee, S. Jeon, W. Jeong, H. Kim, S. C. Gong, H. J. Chang, H. Park, and H. Jeon: *Semicond. Sci. Technol.*, **24** (2009) 035015.

- <sup>58)</sup> D. H. Levy, D. Freeman, S. F. Nelson, P. J. Cowdery-Corvan, and L. M. Irving: *Appl. Phys. Lett.*, **92** (2008) 192101.

- <sup>59)</sup> S. J. Lim, S. J. Kwon, H. G. Kim, and J. S. Park: *Appl. Phys. Lett.*, **91** (2007) 183517.

# 第2章 ALD 法による ZnO 薄膜の形成および評価

## 2.1 緒言

現在、一般的にディスプレイ駆動用 TFT のチャネル層には非晶質シリコン (a-Si:H)や多結晶シリコン(poly-Si)が使用されている。1) しかしながら、これらの材料 は OLED や高精彩ディスプレイに代表される次世代ディスプレイの駆動回路に用い るにあたり、いくつかの課題が挙げられる。1-3) poly-Si を使用した TFT では、50  $cm^2V^{-1}s^{-1}$ 以上の高い電界効果移動度が得られるが、高温のプロセスが必要になる、大 面積への形成が困難であるといった課題がある。<sup>2)</sup>これらの問題により、poly-Si TFT をフレキシブル基板上へ作製することが困難となっている。一方、a-Si:H TFT は既に 大面積フラットパネルディスプレイに使用されているが、低移動度( $\sim 1 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$ )や 使用による電気的ストレス下での特性の劣化等の問題から、次世代ディスプレイへの 適用は難しいと考えられる。4)近年、TFTのチャネル層の材料として ZnO が注目さ れている。ZnO はワイドバンドギャップ(~3.37eV)であることから、可視光領域で透明 であり、また、大面積に良質な膜の低温での形成が可能であることから、プラスチッ クなどのフレキシブル基板への形成にも適している。<sup>4-6)</sup> ZnO TFT は a-Si:H TFT に比 べて高い電界効果移動度が得られることが近年報告されている。<sup>4-9)</sup> しかしながら、 TFT 特性を得るためには ZnO TFT 作製プロセスにおいて高温の熱処理が必要である ため、プラスチック基板へのフレキシブル素子の形成が困難になっている。<sup>10-12)</sup>

原子層堆積(ALD)法は、薄膜形成手法の一つとして LSI の分野で広く使用されている。ALD により堆積された膜は、原料ガスの交互供給により、詳細な膜厚の制御が可能であり、大面積に対し高い均質性、均一性を持つことから注目されている。 $^{13)}$  さらに、ALD により堆積した  $^{2}$  ZnO 薄膜をチャネル層に用いた  $^{2}$  TFT が高い電界効果移動度を示すことが報告されている。 $^{14-17)}$  しかしながら、ALD による  $^{2}$  ZnO 膜の電気的特性は一般的に、高い残留キャリア濃度や導電性等の課題がある。 $^{16)}$  ZnO 膜における高いキャリア濃度は、酸素空孔の様な欠陥が原因となることが知られている。そのため、TFT 特性を得るためや特性の向上には、高い堆積温度や、高温での熱処理、またはドーピングによるキャリアの制御が必要とされる。 $^{14-17)}$

本章では、高い電気的特性を得るため ALD により堆積した ZnO 膜をチャネル層として TFT を作製し、その特性を評価することにより、ZnO TFT 特性の変化の原因解明を試みた。

## 2.2 TFT 特性評価方法 <sup>18-20)</sup>

## 2.2.1 電界効果移動度( μ<sub>FE</sub> )

TFT の特性評価には、出力特性と入力(伝達)特性を用いる。出力特性とは、ゲート(G) - ソース(S) 間電圧( $V_{gs}$ )を一定とし、ドレイン(D) - ソース間電圧( $V_{ds}$ )を 0V から正電圧方向へスイープした場合に流れるドレイン - ソース間電流( $I_{ds}$ )を測定したものである。また伝達特性とは、上記の  $V_{ds}$ と  $V_{gs}$ が入れ替わり、ある一定の  $V_{ds}$ で  $I_{ds}$ を  $V_{gs}$ に対してプロットしたものをいう。デバイスの性能は伝達特性から導かれる電界効果移動度で議論されることが多い。この電界効果移動度は、デバイス構造や用いた材料、測定条件によって変化する特性を校正した値であると言うことができ、様々な TFT の性能を比較することができる。まず、 $V_{ds}\sim 0$  V <  $V_{gs}$  における特性を取り上げる。この領域は線形領域と呼ばれ、物理的に妥当であり、デバイス特性評価としてわかりやすい。また、電界効果移動度の電界強度依存性を無視することができ、ホットキャリアや自己発熱による劣化がないため、測定による劣化を無視できる。ここで、 $I_{ds}$  は

$$I_{ds} = \kappa \left\{ \left( V_{gs} - V_{th} \right) V_{ds} - \frac{1}{2} V_{ds}^2 \right\}$$

(2-1)

$$=\frac{\mu_{lin}W\varepsilon_{o}\varepsilon_{i}}{Lt_{i}}\left\{\left(V_{gs}-V_{th}\right)V_{ds}-\frac{1}{2}V_{ds}^{2}\right\} \tag{2-2}$$

のように表される。

$\mu_{lin}$ は線形領域における電界効果移動度であり、 $V_{th}$  は後に述べる閾値電圧を示す。また、 $\kappa = \mu\left(\frac{w}{L}\right)c_i$ であり、Wはチャネル幅、Lはチャネル長を示し、 $c_i$ はゲート絶縁膜のキャパシタンス、 $t_i$ はゲート絶縁膜厚、 $\varepsilon_o$ ,  $\varepsilon_i$ はそれぞれ真空の誘電率とゲート絶縁膜の比誘電率である。

ここで、 $\frac{\partial I_{ds}}{\partial V_{gs}}$ を計算すると、

$$\mu_{lin} = \frac{L t_i}{W \varepsilon_o \varepsilon_i V_{ds}} \left( \frac{\partial I_{ds}}{\partial V_{gs}} \right) = \frac{g_m}{\frac{W}{L} c_i V_{ds}}$$

(2-3)

となる。

このうち、線形グラフの傾き $\frac{\partial I_{dS}}{\partial V_{gS}}$ が最大のところでの値を用いて算出し、TFT の電界効果移動度  $\mu_{FE}$  とする。しかし、この領域では、S/D 電極とチャネル層の接触

抵抗が高い場合、 $I_{ds}$  が小さくなるため測定が不可能であるという欠点がある。このような場合には  $V_{ds}$  に十分高い電圧(i.e.  $V_{ds}=10$  V)を印加し、測定した結果に飽和領域の式を用いて電界効果移動度を算出し、 $\mu_{FE}$  とする。飽和領域の電界効果移動度( $\mu_{sat}$ )の算出式は

$$I_{ds} = \frac{\mu_{sat} W c_i}{2L} (V_{gs} - V_{th})^2$$

(2-4)

より、 $\frac{\partial I_{ds}}{\partial V_{gs}}$ を計算し、 $(V_{gs}-V_{th})$ を上式へ代入して変形すると、

$$\mu_{sat} = \frac{L t_i}{W \varepsilon_o \varepsilon_i 2 I_{ds}} \left( \frac{\partial I_{ds}}{\partial V_{gs}} \right)^2 = \frac{g_m^2}{2 \frac{W}{I_s} c_i I_{ds}}$$

(2-5)

となる。

このうち、 $\sqrt{I_{ds}}$ の傾き $\frac{\partial \sqrt{I_{ds}}}{\partial V_{gs}}$  が最大のところでの値を用いて算出する。

この時、電界効果移動度を算出した $V_{gs}$ の値が $V_{gs}$ - $V_{th}$ < $V_{ds}$ となり、飽和条件になっていることを確認する。ただし、S端から D端までの電界強度が一定でなく、劣化も生じる可能性があるため物理的に複雑である点に注意する必要がある。

#### 2.2.2 閾値電圧 ( V<sub>th</sub> )

TFT における閾値電圧( $V_{\rm th}$ : Threshold voltage )には、さまざまな定義があり、その目的により使い分けられている。もっとも一般的な定義としては、TFT の伝達特性において  $I_{ds}$  が流れ始める時の  $V_{gs}$  を示す指標であり、 $I_{ds}$  がログスケールで急峻に立ち上がる  $V_{gs}$  を表す。電界効果移動度を求めたところの  $V_{gs}$ ,  $V_{ds}$ ,  $I_{ds}$  の値を用いて、それぞれ次の式に当てはめて算出する。

線形領域では、

$$I_{ds} = \kappa \left\{ \left( V_{gs} - V_{th} \right) V_{ds} - \frac{1}{2} V_{ds}^2 \right\}, \tag{2-6}$$

$$V_{th} = V_{gs} - \frac{1}{2}V_{ds} - \frac{I_{ds}}{\kappa V_{ds}}$$

(2-7)

の式を用いる。

また、飽和領域では

$$I_{ds} = \frac{\mu_{sat}Wc_i}{2L}(V_{gs} - V_{th})^2, \tag{2-8}$$

$$V_{th} = V_{gs} - \sqrt{\frac{2I_{ds}}{\kappa}} \tag{2-9}$$

となる。

また、実用的な  $V_{\rm th}$ の定義方法として、Wや L などのデバイスのパラメータなどを考慮しながら、伝達特性において一定の電流値をとるときのゲート電圧  $V_{\rm gs}$  を  $V_{\rm th}$  とする場合がある。上記の方法で算出不可能な場合、もしくは  $V_{\rm th}$  のシフト量などを検討する場合等に用いられる例として、規格化されたドレイン電流 $I_{\rm ds}=1$  nAにおける  $V_{\rm gs}$  の値などと定義される。特に TFT の伝達特性の閾値下領域に階段状のハンプが現れた場合には、上記の式で導いた値では正確な議論ができない。ここで、規格化する電流値は ON/OFF 比のほぼ中間にあたる桁として求めるが、基本的にはハンプを避けた点での議論が必要になる。さらに、 $I_{\rm ds}$  の線形グラフの傾きが最大の点で接線を引き、接線が x 軸に交わった時の  $V_{\rm gs}$  を  $V_{\rm th}$  とする場合もある。また、 $V_{\rm th}$  は  $N_{\rm t}$  を用いて

$$V_{th} = \frac{q}{c_i} N_t \tag{2-10}$$

と表される。ここで $N_t$ は半導体薄膜中の捕獲キャリア密度であり、従って、 $V_{th}$ が半導体薄膜中の捕獲準位密度に影響されて変化することが解る。

以上のように、TFT においては通常の MOSFET と異なり、さまざまな定義があるため、どの定義を適用したかを明記する必要がある。本研究では、伝達特性においてドレイン電流が  $1\,\mathrm{nA}$  となる時の  $V_\mathrm{gs}$ を  $V_\mathrm{th}$  とした。

#### 2.2.3 サブスレッショルドスイング (S値)

サブスレッショルドスイング(S 値: Subthreshold swing)は、伝達特性のオフ領域からオン領域へと遷移する閾値下領域において、 $I_{ds}$  が 1 桁増加し 10 倍になるときに要する  $V_{gs}$  の電圧差を示す。S 値を算出する式は一般的に

$$S = \ln(10) \frac{\partial V_{gs}}{\partial (\ln(I_{ds}))}$$

(2-11)

と表される。ここで、式(2-11)と

$$I_{ds} = \kappa (V_{gs} - V_{th})V_{ds} \tag{2-12}$$

を用いて変形すると、

$$S = \ln(10) \frac{1 - \left\{ \frac{\emptyset_{fr}}{V_{gs}} + \left( \frac{c_i}{q} \right)^{-1} \left( D_{fr} \frac{\emptyset_{fr}}{V_{gs}} + D_{bk} \frac{\emptyset_{bk}}{V_{gs}} \right) \right\}}{1 - \left\{ \frac{\emptyset_{fr}}{V_{gs}} + \left( \frac{c_i}{q} \right)^{-1} \left( D_{fr} \frac{\partial \emptyset_{fr}}{\partial V_{gs}} + D_{bk} \frac{\partial \emptyset_{bk}}{\partial V_{gs}} \right) \right\}} V_{gs}$$

(2-13)

となり、 $D_{fr}$ 、 $D_{bk}$ はそれぞれ表面界面捕獲準位密度、裏面界面捕獲準位密度であり、 $\phi_{fr}$ 、 $\phi_{bk}$ はそれぞれ表面、裏面のポテンシャルバリアである。これにより、S 値は界面準位密度に依存して変化し、S 値を低減するためには  $D_{fr}$ 、 $D_{bk}$  を低減すればよいことがわかる。S 値が小さいほど特性は急峻な立ち上がりとなり、スイッチング特性が良いといえる。

## 2.3 ALD による ZnO 薄膜の酸化剤による TFT 特性比較

#### 2.3.1 ALD による ZnO 薄膜の形成

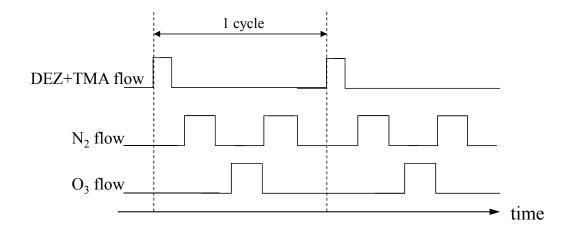

本実験では、ALD 法により低温形成した ZnO 膜を用いて TFT を作製し、ZnO TFT の低温プロセス化を試みた。ZnO 膜成膜のための Zn 原料としてジエチルジンク (  $DEZ: Diethyl \, Zinc, (C_2H_5)_2Zn$  )、パージガスとして  $N_2$  ガスを用いた。ALD により 低温形成した ZnO 膜の TFT への応用において、一般的に課題となっている原料酸化 不足に起因する残留不純物、過剰残留キャリアの低減のための手法として、反応の活性化にプラズマを援用する PA-ALD の適用を提案し、従来の熱 ALD 法による ZnO 膜と比較することによりその有用性を評価した。成膜におけるタイムチャートを図 2-1 に示した。酸化剤として、熱 ALD による成膜では  $H_2O$  (  $H_2O-ALD$  )、PA-ALD では、酸素ガスにプラズマを印加したプラズマ酸素を用いてそれぞれ成膜を行い、酸化剤の違いによる特性の変化を比較した。ZnO 膜の評価においては、X 線光電子分光 ( $XPS: X-ray \, Pa-ray \, Pa-r$

図 2-1. ALD 法による ZnO 膜堆積タイムチャート

## 2.3.2 ZnO TFT 作製プロセス

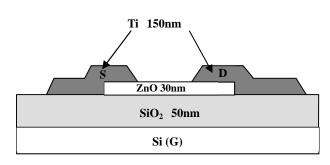

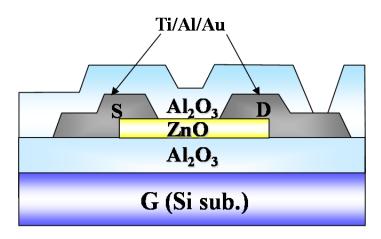

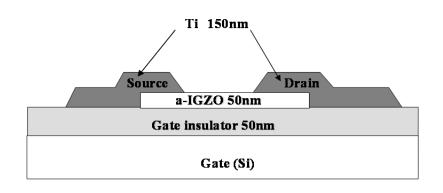

本研究で作製したボトムゲート型 ZnO TFT の断面図および作製プロセスを図 2-2、図 2-3 にそれぞれに示す。p型 Si (001) 基板をゲート (G) 電極として用い、ゲート絶縁膜として SiO<sub>2</sub>を 50 nm、熱酸化により形成した。この基板上に、チャネル層として ZnO 膜を 30 nm、ALD により堆積し、フォトリソグラフィ技術を用いてウェットエッチングによりパターニングを行った。ソース/ドレイン (S/D) 電極として Ti を用い、リフトオフによりパターニングし、図 2-2 に示すようなボトムゲート型 TFT を作製した。

図 2-2. ボトムゲート型 ZnO TFT

図 2-3. ボトムゲート型 ZnO TFT 作製プロセス

## 2.3.3 ホール効果測定

$H_2O$ -ALD および PA-ALD により堆積した ZnO 膜の電気的特性を、Hall 効果 測定により測定した。ここでは、van der Pauw 法を用いた Hall 効果測定(ケースレー、RESITEST - 8300)の測定結果から、キャリア密度を調べた。成膜温度を  $100\sim300$   $^{\circ}$  で化させた時の、比抵抗およびキャリア濃度の測定結果を表 2-1 に示す。

PA-ALD で作製した ZnO 膜は比抵抗値の測定上限である  $1\times10^3$   $\Omega cm$  より高く、正確な値は測定できなかった。キャリア濃度も同様に、測定下限以下の値を示した。一方、 $H_2O$ -ALD により成膜された ZnO 膜は PA-ALD と比較して比抵抗値は大きく低減され、それに伴い高いキャリア濃度を示した。さらに、 $H_2O$ -ALD による抵抗の低い試料を  $300^{\circ}$  C程度の酸素雰囲気中で熱処理することにより、比抵抗が上がるという結果が得られた。このことから酸素欠損による余剰電子がキャリアとなっていると考えられる。

以上の結果から、TFT への応用の際に必要とされる特性に対して、ZnO 膜の電気的特性に成膜温度の変化による大きな変化や改善は見られなかった。このことから、本研究の目的であるプラスチックなどのフレキシブル基板上へのデバイス作製を目指した低温プロセス化のため、ALD 成膜プロセス温度を100℃とした。

|                      | Deposition temperature [ $^{\circ}$ C] | Resistivity [Ωcm]    | Career concentration [/cm³] |

|----------------------|----------------------------------------|----------------------|-----------------------------|

| H <sub>2</sub> O-ALD | 100                                    | 1.7×10 <sup>-1</sup> | 2.1×10 <sup>19</sup>        |

|                      | 200                                    | 1.5×10 <sup>-2</sup> | 7.8×10 <sup>19</sup>        |

|                      | 300                                    | 1.1×10 <sup>-3</sup> | 5.1×10 <sup>21</sup>        |

| PA-ALD               | 100                                    | $> 1 \times 10^3$    | <1×10 <sup>17</sup>         |

|                      | 200                                    | $> 1 \times 10^{3}$  | <1×10 <sup>17</sup>         |

|                      | 300                                    | $> 1 \times 10^{3}$  | <1×10 <sup>17</sup>         |

表 2-1. Hall 効果測定結果

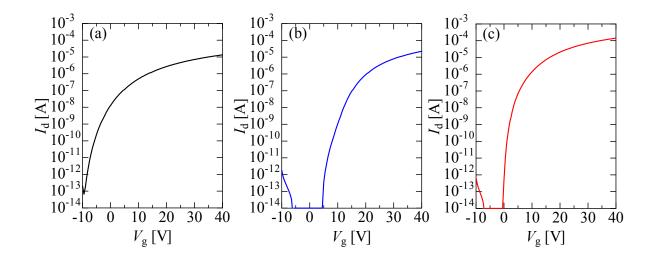

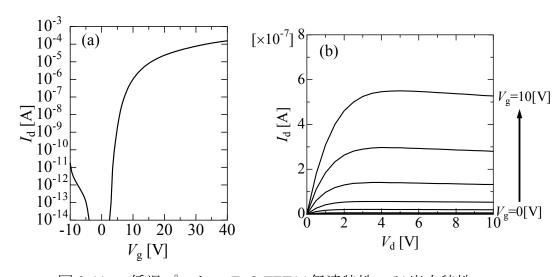

#### 2.3.4 ZnO TFT 伝達特性

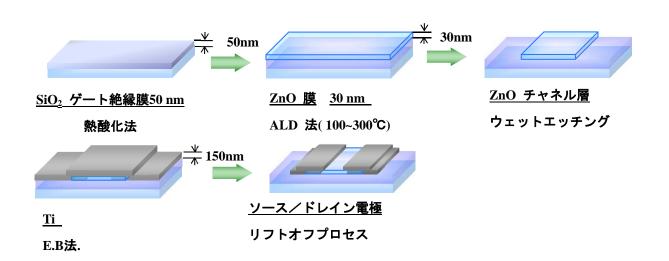

$H_2O$ -ALD および PA-ALD により、基板温度  $100^{\circ}$ Cで堆積した ZnO 膜を用いて作製した TFT に熱処理を行い、 $V_d=5$  V を印加した時の伝達特性を測定した。熱処理条件は酸素雰囲気( $O_2=20$  %,  $N_2=80$  %)中、 $300^{\circ}$ Cで 1 時間とし、熱処理前後の伝

達特性の測定結果を図 2-4 (a), (b) にそれぞれ示す。また、熱処理温度を 100<sup> $\circ$ </sup> たから 400<sup> $\circ$ </sup> こまで変化させた時の on/off 比の変化を図 2-4(c)に示す。

図 2-4 (a) の破線で示すように、 $H_2O$ -ALD で堆積された ZnO 膜を使用した TFT ( $H_2O$ -ALD ZnO TFT) は、熱処理なしではスイッチング特性を示さなかった。さらに、伝達特性は図示していないが、200  $^{\circ}$   $^{$

図 2-4. ZnO TFT 伝達特性 (a)熱処理前、(b)300 $^{\circ}$ 熱処理後、(c)熱処理温度に対する on/off 比の変化( $V_d$ = 5 V)

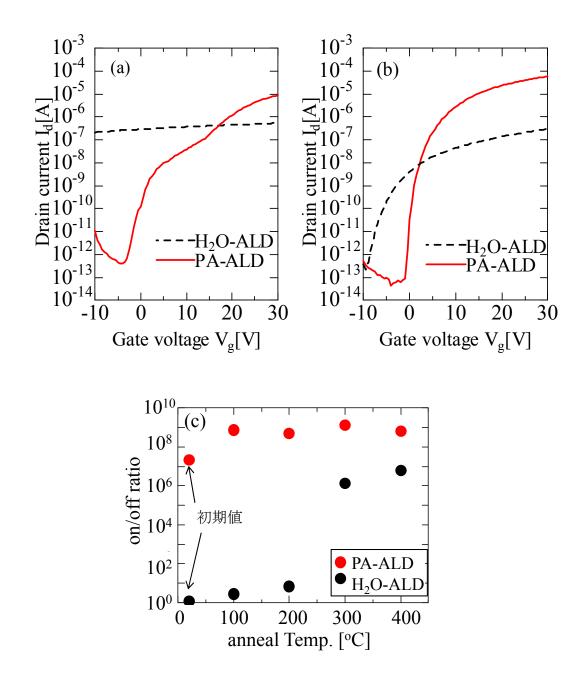

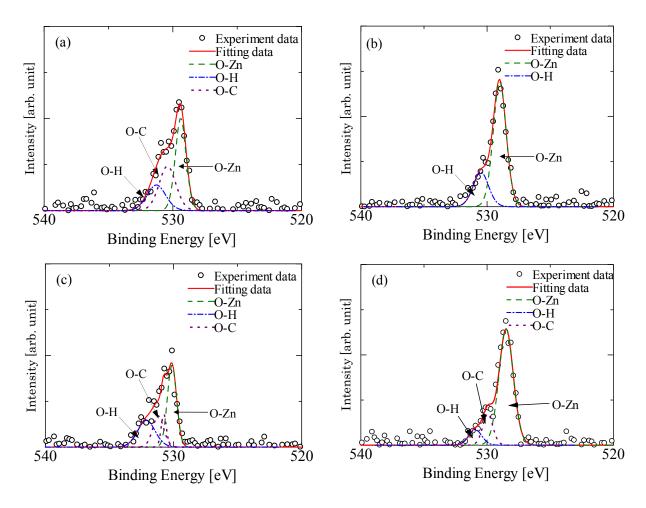

## 2.3.5 X線光電子分光による ZnO 膜の組成評価

PA-ALD による電気的特性の向上の原因を調べるため、XPS により基板温度  $100^{\circ}$  で成膜された ALD-ZnO 膜の組成の測定を行った。酸素雰囲気中で、熱処理温度 を  $100^{\circ}$  化させたときの酸素 (O)、炭素 (C) の ZnO 膜中における原子濃

度の測定結果を図 2-5 に示す。

$H_2O$ -ALD による ZnO 膜は、PA-ALD に比べ低い酸素濃度を示し、 $H_2O$ -ALD ZnO 膜中の炭素濃度は、PA-ALD に比べ高い値を示した。この  $H_2O$ -ALD ZnO 膜中の酸素濃度は、300<sup>°</sup>C以上の熱処理により増加し、また、炭素濃度は減少した。これは、成膜時の残留炭素に起因する酸素欠陥が、熱処理により低減されたためであると考えられる。

これらの測定結果と、前項で示した ALD-ZnO TFT の電気特性とを比較すると、スイッチング特性を示さなかった熱処理前、および  $200^{\circ}$ C以下での熱処理の  $H_2O$ -ALD ZnO TFT は、ZnO 膜の亜鉛過多(Zn-rich)の状態となり、余剰分子が過剰キャリアとなったものであると考えられる。 さらに、低い  $I_{d_on}$  などの不十分な TFT デバイス特性は、DEZ の酸化不足による ZnO フィルム中の残留炭素によるものであると思われる。

以上の結果から、PA-ALD を用いることにより、ZnO TFT の作製プロセスの 低温化が可能であることが示唆された。

図 2-5. 酸素中熱処理温度の変化による ALD-ZnO 膜中 O および C 濃度 測定結果

図 2-6. XPS (O 1s)測定結果 (a) PA-ALD (熱処理前)、(b) PA-ALD (300℃熱処理後)、(c) H<sub>2</sub>O-ALD (熱処理前)、(d) H<sub>2</sub>O-ALD (300℃熱処理後)

## 2.4 ZnO TFT 特性における熱処理の効果

## 2.4.1 熱処理による ZnO TFT 伝達特性の変化

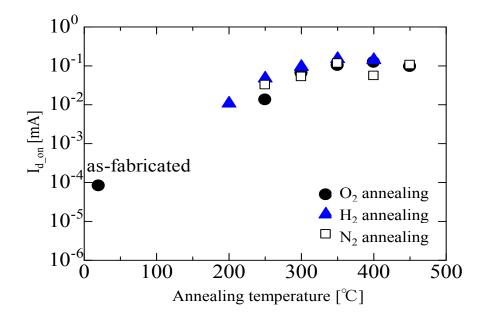

第2章3節で示された結果を用いて、PA-ALDにより堆積されたZnO膜を使 用して TFT を作製し、温度を 200  $\sim$ 450 $^{\circ}$ 、雰囲気ガスを酸素雰囲気  $(O_2 = 20\%, N_2)$ =80%)、水素雰囲気( $H_2=10\%$ ,  $N_2=90\%$ )、窒素雰囲気( $N_2=100\%$ )と変化さ せ、それぞれ 1 時間の熱処理を行った。この時の、温度変化に対する  $I_{d_{on}}$  の測定結 果を図2-7に示す。全ての雰囲気で、熱処理温度の上昇により $I_{d_{-}m}$ は増加し、これに より電界効果移動度もまた増加した。しかし、窒素雰囲気中での熱処理では、温度上 昇に対する特性の変化にばらつきがみられ、水素雰囲気中での熱処理では、高い電界 効果移動度は得られたが、温度の上昇とともに $V_{th}$ のネガティブシフトやS値の悪化 がみられた。ZnO TFT において、 $V_{th}$  のネガティブシフトは ZnO 膜中の酸素欠損に 起因すると考えられる。<sup>22)</sup>このことから、還元雰囲気である水素雰囲気中で熱処理 を行うことにより ZnO 膜中の酸素が積極的に還元され、これにより膜中の酸素欠損 が増加し、 $V_{\rm th}$ のシフトに繋がったと考えられる。また、 ${

m ZnO}$  は酸素欠損の生成され やすい材料であることが知られている。<sup>22)</sup>このため、窒素雰囲気での熱処理におい ても酸素の脱離が生じたが、還元雰囲気である水素雰囲気に対し窒素ガスは不活性ガ スであるため、窒素雰囲気中での熱処理では再現性の低い結果となったと考えられる。 一方、酸素雰囲気中での熱処理では、温度の上昇に対し安定して TFT 特性の向上が みられた。これは、膜中の欠陥が熱処理雰囲気中の酸素により補償されたためである と考えられる。

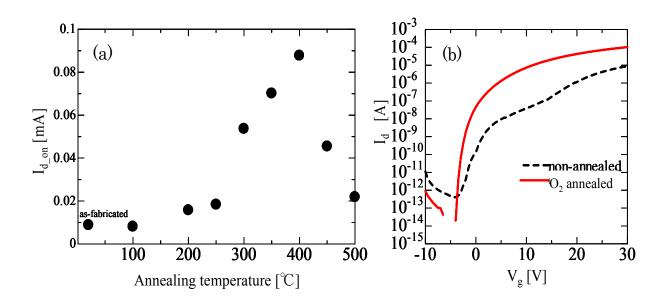

この結果から、作製した PA-ALD ZnO TFT を、酸素雰囲気中で温度を  $100 \sim 500$ °Cに変化させ熱処理を行い、特性の変化を詳細に調べた。 1 時間熱処理した時の熱処理温度の変化に対する  $I_{d_on}$  の測定結果を図 2-8(a)に、350°Cで 1 時間の熱処理をした時の、熱処理前後での伝達特性を図 2-8(b)にそれぞれ示す。図 2-8(a)に示すように、 $I_{d_on}$  は 200 °C以上の熱処理で増加しはじめ、450°C以上の熱処理で減少した。この 450 °C以上での  $I_{d_on}$  の減少は、S/D 電極として使用している Ti の酸化により、抵抗が増加したためであると思われる。350°Cで 1 時間の熱処理を行った ZnO TFTでは、図 2-8(b)に赤の実線で示すように、熱処理前に比べ  $I_{d_on}$  の減少、および  $I_{d_on}$  の増加により、 $5 \times 10^9$  の on/off 比が得られた。この時の電界効果移動度は約  $2.1 \text{ cm}^2/\text{Vs}$ であり、 $V_{th}$  および S 値は、それぞれ -2.1 V および 0.2 V/decade であった。

これらの測定結果から、作製した ZnO TFT を酸素雰囲気中で熱処理することにより、ZnO 膜中の酸素欠損が補償され、トランジスタ特性の向上に寄与したと考えられる。

図 2-7.  $I_{d_on}$ の熱処理温度依存性( $V_d = 5 V$ )

図 2-8. PA-ALD ZnO TFT 伝達特性 (a) 熱処理温度に対する  $I_{d_on}$  測定結果,(b) 350 C熱処理前後の伝達特性( $V_d=5$  V)

## 2.4.2 電気ストレスに対する信頼性評価

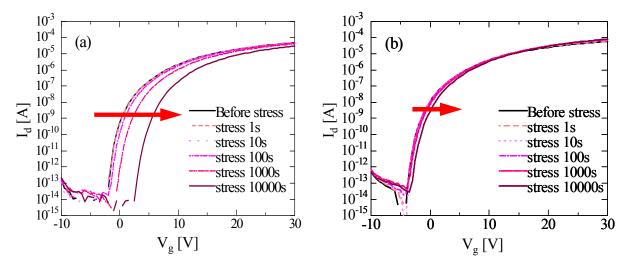

バイアスストレス下での TFT の安定性は、ディスプレイ駆動素子等への応用時に重要となる。デバイスの信頼性評価のため、作製した TFT を酸素雰囲気中で熱処理し、ゲートおよびドレインにそれぞれ  $20\ V$  のバイアスストレスを、室温にて 1, 10, 100, 1000, 10000 秒印加した際の伝達特性を測定した。

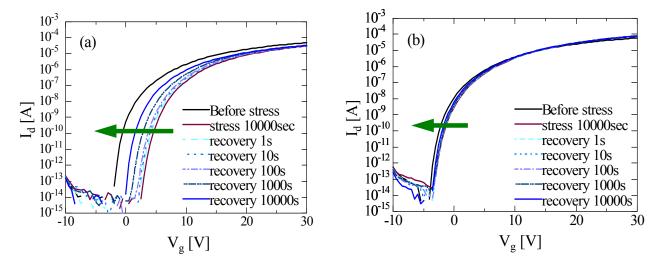

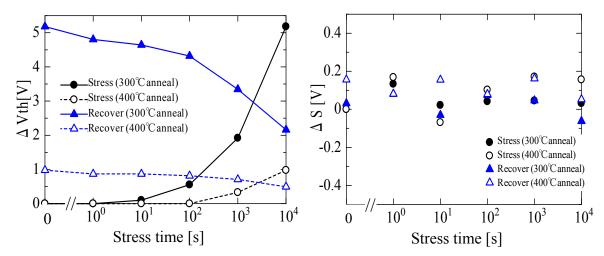

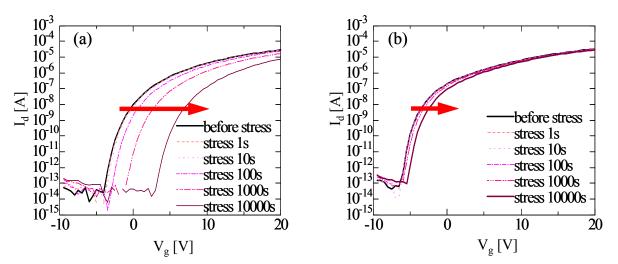

300℃で熱処理した TFT の測定結果を図 2-9(a)に、400℃で熱処理した TFT の測定結果を図 2-9 (b)にそれぞれ示す。図 2-9 (a)に示すように、300℃での熱処理では、ストレス印加により時間経過とともに  $V_{\rm th}$ が大きくポジティブシフトした。一方で、400℃で熱処理した TFT ではこの  $V_{\rm th}$ のシフト( $\Delta$   $V_{\rm th}$ )が大きく低減した。さらに、10000 秒のバイアスストレス印加後、電圧を開放し、室温で放置した際の 1,10,100,1000,10000 秒経過後の伝達特性の変化を図 2-10(a)、(b)に示す。図 2-10 (a)は 300℃での熱処理、図 2-10 (b)は 400℃で熱処理した TFT の時間経過による回復特性を示している。図 2-11 は、ストレス印加および回復による  $\Delta$   $V_{\rm th}$  の時間経過による推移を示しており、10000 秒のバイアスストレス印加によりシフトした  $V_{\rm th}$  は、時間経過とともに熱処理なしで回復した。この回復特性は、 $\alpha$ -Si:H や poly-Si TFT では見られず、劣化した特性の回復には熱処理が必要となる。 $\alpha$ -3,240 また、図 2-11 に示すように、ストレス印加による S 値の変化( $\alpha$ -S はみられなかった。

さらに、ドレインバイアスストレスを 0 V とし、ゲートバイアスを 20 V 印加した際の時間経過による伝達特性の測定結果を図 2-13(a)、(b)に示す。 ゲートバイアスのみを印加した際も、ゲートおよびドレインの両方にストレスを印加した時と同様に、 $V_{th}$  のシフトがみられ、S 値の変化はみられなかった。また、ゲートバイアスストレスを 0 V とし、ドレインバイアスのみを印加した際には、伝達特性にストレス印加による大きな変化はみられなかった。

これらの結果から、電気的ストレス印加による  $V_{\rm th}$  のシフトはゲートバイアスストレスに起因することが示唆された。 ${\rm a} ext{-}{\rm Si}:{\rm H}$  TFT において、直流ゲート電圧印加による  $\Delta V_{\rm th}$  発生の原因として、2 種類のメカニズムが確認されている。準位生成に起因する  $\Delta V_{\rm th}$  ではストレス印加時間のべき乗に依存し、チャージトラップによる $V_{\rm th}$  のシフトは、ストレス印加の対数時間に依存するとされている。 ${}^{25 ext{-}27)}$  このことから、 ${\rm ZnO}$  TFT における電気的ストレスによる  $V_{\rm th}$  のシフトはチャージトラップに起因するものであると考えられる。

図 2-9. ゲート/ドレインバイアスストレス( $V_{\rm g}/V_{\rm d}=20/20$  V)印加による伝達特性の変化 (a)300  $^{\circ}$ C,(b)400  $^{\circ}$ C熱処理 ZnO TFT

図 2-10. バイアスストレス( $V_{\rm g}$  /  $V_{\rm d}$  =20/20 V) 10000 秒印加後の回復特性 (a) 300 °C,(b) 400 °C熱処理 ZnO TFT

図 2-11. 時間経過による  $\Delta V_{\rm th}$  の推移

図 2-12. 時間経過による  $\Delta S$  の推移

図 2-13. ゲートバイアスストレス(Vg= 20 V) 印加による伝達特性の変化 (a)300℃、(b)400℃熱処理後 ZnO TFT

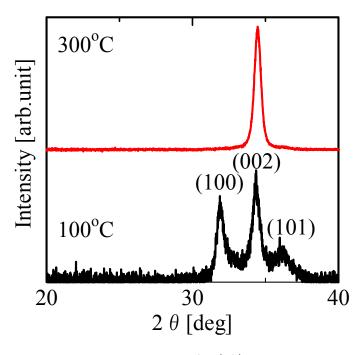

## 2.4.3 X線回折による結晶性評価

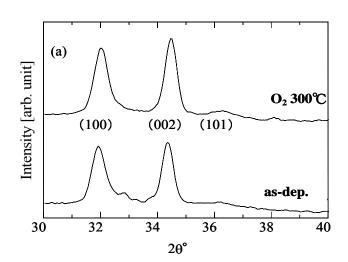

PA-ALD により堆積した ZnO 膜の結晶性を、XRD 測定により評価した。ZnO TFT の作製に用いた ZnO 膜の XRD 測定結果を、図 2-14(a)-(c)に示す。図 2-14(a)の上下はそれぞれ熱処理前および酸素雰囲気中、 $300^{\circ}$ Cで 1 時間の熱処理を行った後の、ZnO 膜の XRD パターンを示している。熱処理後の ZnO 膜では、(100)に比べ、c 軸である(002)のピーク強度がやや強まり、c 軸配向の傾向がみられた。図 2-14(b)は、熱処理温度を  $200\sim400^{\circ}$ Cに変化させたときの、熱処理前および熱処理後の(002)のピ

ークを示している。ZnO 膜の(002)ピークは、熱処理温度の上昇とともに高角度側へシフトする傾向がみられた。熱処理温度に対する(002)ピークの  $2\theta$  の値を図 2-14(c)に示す。この結果から、(002)のピークは熱処理温度 200℃から 300℃でステップ状に変化することが分かった。これは、ZnO TFT における熱処理温度に対する  $I_{d,on}$  の変化と一致する傾向を示している。300℃で熱処理を行った ZnO 膜の、熱処理前後での(002)の  $2\theta$  のピーク値、および測定結果より算出した格子定数 c の値を表 2-2 に示す。熱処理による(002)ピークの高角度側へのシフトにより、格子定数が減少した。その結果、熱処理前と比較して、熱処理を行った ZnO 膜では、ZnO 単結晶の固有値に近づくことが分かった。この格子定数の減少は、成膜の時点では不十分であった ZnO の結合が、本来の安定した状態に回復したことを意味するものであると思われる。

XRD による結晶性の測定結果と、前項で示した熱処理温度の変化による ZnO TFT の伝達特性の測定結果とを比較して、 ZnO TFT の熱処理によるデバイス特性の向上は、チャネル層である ZnO 膜の結晶性の改善も寄与していると考えられる。

表 2-2. XRD 測定結果

|                                  | 熱処理前  | O <sub>2</sub> , 300 ℃<br>熱処理後 | ZnO バルク固有値 <sup>4)</sup> |

|----------------------------------|-------|--------------------------------|--------------------------|

| (002)ピークの 2 $\theta$ [ $\circ$ ] | 34.32 | 34.42                          | 34.422                   |

| 格子定数<br>c[Å]                     | 5.22  | 5.20                           | 5.204                    |

## 2.4.4 ZnO 膜組成評価

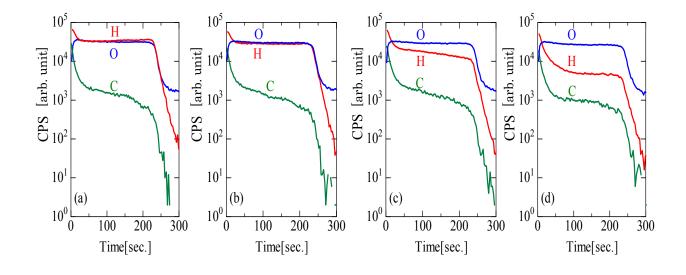

TFT 作製に用いた ZnO 膜の、熱処理による組成の変化を調べるため、SIMS による測定を行った。図 2-15(a) - (d)に、それぞれ熱処理前、酸素雰囲気中で  $200^{\circ}$ C から  $400^{\circ}$ Cの熱処理を行った後の ZnO 膜中の酸素(O)、水素(H)、炭素(C)の測定結果を示す。  $400^{\circ}$ Cで熱処理したサンプルでは、熱処理前のものに比べ水素濃度が大きく減少した。これは、ZnO 膜中の残留水素が熱処理により脱離したためであると考えられる。 SIMS 測定による ZnO 膜中の水素および炭素濃度の測定結果と、ZnO TFT にバイアスストレスを 10000 秒印加した後の閾値の変化量の熱処理温度に対する変化を図 2-15(e)に示す。この結果、熱処理温度の上昇と共に閾値電圧のシフトは低減され、膜中の水素濃度も大幅な減少が見られた。一方で、炭素濃度は熱処理により低減されたが、水素および閾値電圧のシフト量の変化と比較して大きな変化は見られなかった。これらの測定結果から、バイアスストレス印加による TFT 特性の劣化には、水素が要因となっているものと思われる。

図 2-15. (a)熱処理前、(b)200 $^{\circ}$ 、(c)300 $^{\circ}$ 、(d)400 $^{\circ}$ 熱処理後の ALD-ZnO 膜中における O,H,C の SIMS 測定結果、(e)熱処理温度による TFT 信頼性評価及び膜中水素量の測定結果

## 2.5 プラズマ印加時間による ZnO TFT 特性の変化

## 2.5.1 ZnO TFT 伝達特性

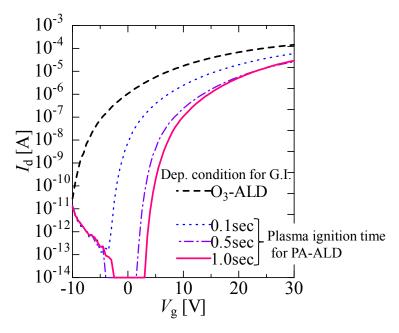

これまでの結果から、反応の活性化にプラズマを援用する PA-ALD 法により、低温で堆積した ZnO 膜においても、TFT の高性能化が可能であることが分かった。これは、金属原料である DEZ が、プラズマの印加により効果的に酸化され、膜中の残留不純物が低減されたためである。そこで、さらなる ZnO TFT の高性能化に向け、ZnO 膜堆積時のプラズマ印加時間による特性への影響を検討した。プラズマ印加時間の変化による ZnO TFT 伝達特性への影響を調べるため、成膜時のプラズマ印加時間を  $0.1\sim1.5$  秒に変化させ、ZnO 膜を堆積した。膜厚 50 nm の熱酸化膜を形成した低抵抗 Si 基板上に、膜厚 30 nm となるよう ZnO 膜を堆積し、堆積温度は 100 とした。

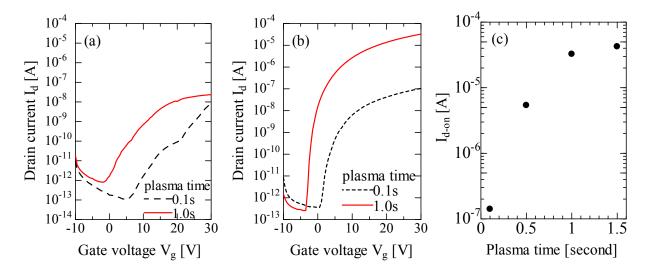

作製した TFT の伝達特性の測定結果を、図 2-16 に示す。図 2-16 (a)および(b) は、プラズマ印加時間 0.1 秒、1.0 秒で堆積した ZnO 膜を使用して作製した TFT の、それぞれ初期値および 300℃で 1 時間の熱処理を行ったものの特性を示している。また、図 2-16 (c)には成膜時のプラズマ印加時間に対する、300℃で熱処理した TFT の伝達特性の on 電流( $I_{d_con}$ )の変化を示す。ここで、on 電流はゲート電圧を-10 から 30 で測定した際の、ドレイン電流の最大値とする。プラズマ印加時間 0.1 秒、1.0 秒の ZnO 膜を用いた TFT は、共に TFT 作製後の熱処理なしでスイッチング特性を示した。しかしながら、プラズマ印加時間 0.1 秒の ZnO 膜を使用した TFT では、 $I_{d_con}$ 、電界効果移動度は共に低く、熱処理を行った後でも TFT 特性はスイッチング素子として不十分なものであった。一方、プラズマ印加時間 1.0 秒の ZnO 膜を使用した TFT では、300℃の熱処理後、 $1\times10^8$ .以上と非常に高い on/off 比を示した。この時の電界効果移動度は約 3.2 cm $^2$ V $^1$ s $^1$ 、閾値電圧は-1.3 V であり、S 値は 0.3 V/decade であった。プラズマ印加時間をさらに延長したが、1.0 秒以上の印加では特性はほぼ飽和し、大きな変化は見られなかった。

作製した TFT の測定結果から、PA-ALD による ZnO TFT のデバイス特性はプラズマ印加時間の延長と共に向上し、1.0 秒の印加で高い電界効果移動度および on/off 比が得られることが分かった。

図 2-16. プラズマ印加時間 0.1 秒、1.0 秒で堆積した ZnO TFT  $\mathcal{O}(a)$ 初期値および(b)300℃熱処理後の伝達特性、(c)プラズマ印加時間 0.1-1.5 秒での  $I_{d_{on}}$ の変化

## 2.5.2 ZnO 薄膜特性

プラズマ印加時間の変化による TFT 特性の変化の原因を調べるため、ZnO 膜の特性を評価した。チャネル層である ZnO 膜の膜質の向上が ZnO TFT の特性向上につながると考えられるため、ZnO 膜の密度および膜内の残留不純物量の変化を調べた。

不純物や欠陥多い等の原因により低密度となった膜では、膜の屈折率が低くなるという報告がされている  $^{28,29)}$ 。そこで、プラズマ印加時間の延長による ZnO 膜の密度の変化を調べるため、ZnO 膜の屈折率を評価した。測定には分光エリプソメトリ(  $HORIBA\ JOBIN\ YVON$ ,  $UVISEL\ ER\ AGMS-NSD$  )を使用し、ZnO 膜の屈折率および  $1\$ サイクルあたりの成膜レートを調べた。

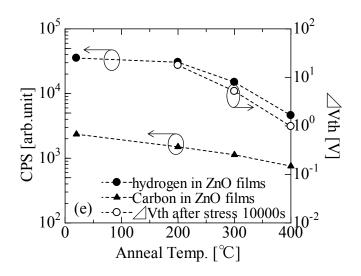

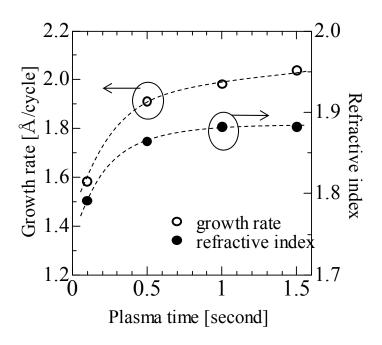

プラズマ印加時間に対する、ZnO 膜の堆積レートおよび屈折率の測定結果を図 2-17 に示す。1 サイクルあたりの堆積レートと ZnO 膜の屈折率は、プラズマ印加時間の延長と共に増加し、1 秒以上の印加でほぼ飽和する傾向が見られた。プラズマを 0.1 秒印加した時の堆積レートは 1.5 Å/cycle であり、1.0 秒以上では 2.0 Å/cycle であった。c 軸配向した単結晶 ZnO の 1 原子層の厚さは約 2.5 Åであり、Zn-O 間の距離は 1.99 Åである。本研究における ZnO 膜は多結晶であるため、詳細な 1 層あたりの膜厚の特定は不可能であるが、1 原子層あたりの ZnO 膜の厚さはおよそ 2.0-2.5 Åと見積もられる。30 プラズマ印加時間が 0.5 秒以下での成膜においては、1 サイクル辺りの膜厚がこの値に達していない結果となった。このことから、0.5 秒以下のプ

ラズマの印加では金属原料である DEZ の酸化が不十分であり、1 サイクルで 1 層の成膜が行われていないと考えられる。一方で、1 秒以上プラズマを印加した膜では 1 サイクル辺りの膜厚が、見積もられた 1 層辺りの厚さに達し、飽和する傾向を示した。この結果から、プラズマ印加時間の延長により酸化が十分に行われたと考えられる。

また、ZnO 単結晶の屈折率の固有値は、1.9-2.0 である。しかしながら、プラズマ印加時間 0.1 秒で堆積した ZnO 膜の屈折率は、1.8 以下であり、高純度 ZnO よりも低密度であることが示された。これらの結果から、金属原料である DEZ の酸化には 0.5 秒以上のプラズマ印加が必要であることが分かった。プラズマを 1.0 秒以上印加し堆積した膜は、プラズマ印加時間 0.1 秒の膜よりも高い屈折率を示した。分光エリプソメトリの測定結果から、PA-ALD による ZnO 膜堆積時にプラズマを十分に印加することにより、ZnO 膜の密度を向上させられることが分かった。このことから、二次イオン質量分析法(SIMS: Secondary Ion Mass Spectroscopy) を使用して ZnO 膜の元素分布分析を行い、ZnO 膜の低密度の原因の特定を試みた。

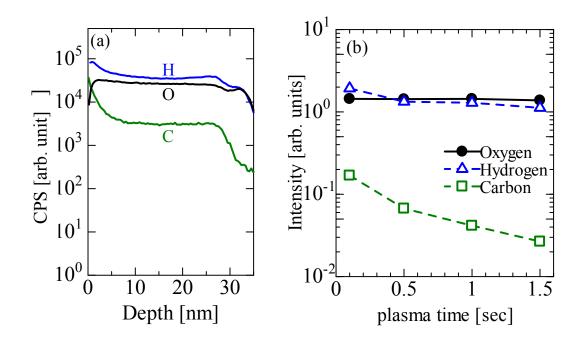

SIMS 測定は、堆積後の熱処理をしていない ZnO 膜に対して行い、膜中の酸素(O)、水素(H)、炭素(C)を測定した。プラズマ印加時間 0.1 秒で堆積した膜の測定結果を図 2-18 (a)に示す。図 2-18 (b)は、プラズマ印加時間に対する膜中元素の測定結果の変化を示している。各元素の Intensity は、ZnO 膜を堆積したシリコン基板の Si の測定値に対する、ZnO 膜の深さ 10-20 nm における各元素の測定値の平均値の比で示している。膜中の水素および炭素濃度は、プラズマ印加時間の延長と共に減少した。この水素および炭素は、金属原料である DEZ に起因する残留不純物であり、残留炭素および水素は DEZ の堆積時の酸化不足によるものであると考えられる。

分光エリプソメトリによるプラズマ印加時間に対する ZnO 膜の屈折率の測定結果と、SIMS による膜中元素分析の結果を比較して、膜中の残留炭素および水素が ZnO 膜の密度を低下させると考えられる。プラズマ印加時間の延長による ZnO TFT 伝達特性の向上は、ZnO 膜中の残留不純物の低減による膜質の向上が一因として考えられる。

図 2-17.プラズマ印加時間 0.1-1.5 秒での ZnO 膜の堆積レートおよび屈折率

図 2-18. SIMS 測定結果 (a)プラズマ印加時間 0.1 秒で堆積した ZnO 膜の O、H、C 測定結果 (b) プラズマ印加時間 0.1-1.5 秒での O、H、C の平均値

## 2.6 PA-ALD による ZnO TFT 特性における堆積温度依存性

## 2.6.1 PA-ALD による ZnO TFT 伝達特性

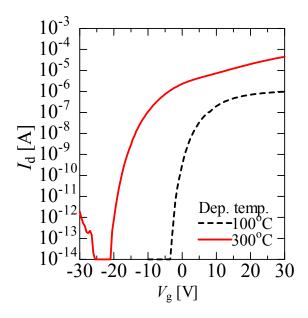

ZnO 薄膜堆積時の堆積温度に対する、ZnO TFT 特性の変化を調べるため、PA-ALD により堆積温度 100 C および 300 C で ZnO 薄膜を形成した。熱酸化により形成した  $SiO_2$  薄膜をゲート絶縁膜とし、ZnO TFT を作製し、熱処理なしでの特性を評価した。図 2-19 は、作製した TFT の  $V_d=5$  V での伝達特性を示している。堆積温度 100 C および 300 C での ZnO TFT は共に、熱処理なしでスイッチング特性を示した。 さらに、300 C で堆積した ZnO 膜を使用した TFT では、100 C で堆積したものに比べ、電界効果移動度の増加など、特性の向上がみられた。堆積温度 300 C の TFT における on/off 比は $>10^9$  であり、電界効果移動度は 5.7 cm $^2$ V $^{-1}$ s $^{-1}$  であった。

これまでの実験結果から、ALD により堆積した ZnO 膜を用いた TFT の特性の向上は、ZnO 膜中の残留不純物の低減および ZnO 膜の結晶性の向上が原因と考えられる。そのため、堆積温度に対する ZnO 膜の特性の変化を調べた。

図 2-19. ZnO TFT 伝達特性 (V<sub>d</sub>=5 V)

## 2.6.2 X 線回折による ZnO 膜の結晶性評価

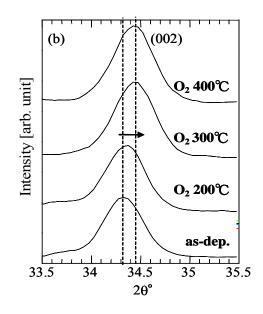

堆積温度に対する ZnO TFT 特性の変化の原因を調べるため、まず XRD により ZnO 膜の結晶性を評価した。図 2-20 に、TFT のチャネル層に使用した ZnO の XRD 測定結果を示す。 $100^{\circ}$ Cで堆積した ZnO 膜では、(100)、(002)、(101)の 3 つのピークがみられた。一方、 $300^{\circ}$ Cで堆積した ZnO 膜は(002)のみのピークを示し、基板に対して垂直な c 軸優先配向の膜が形成されていることが分かった。ZnO 膜は多結晶であり、多結晶半導体薄膜を使用した TFT では、結晶粒界における欠陥準位や散乱等、粒界からの影響が on 特性および電界効果移動度の低減の原因の一つとして挙げられる。このことから、ZnO 膜堆積温度の上昇により配向が揃ったことで粒界からの影響が低減されたため、ZnO 膜堆積温度の上昇により配向が揃ったことで粒界からの影響が低減されたため、ZnO 原本の上記のでは、ZnO 原本の正式のでは、ZnO 原本の正式ので、ZnO 原本の正式ので、ZnO 原本の正式ので、ZnO 原本の正式ので、ZnO 原本の正式ので、ZnO 原本の正式ので、ZnO 原本の正式ので、ZnO 原本の正式ので、ZnO を可能のでは、ZnO を表述ので、ZnO 原本の正式ので、ZnO を述述ので、ZnO を述述ので、ZnO を述述ので、ZnO を述述ので、ZnO を述述ので、ZnO を述述ので、ZnO を述述ので、ZnO を述述ので、Z

図 2-20. XRD 測定結果

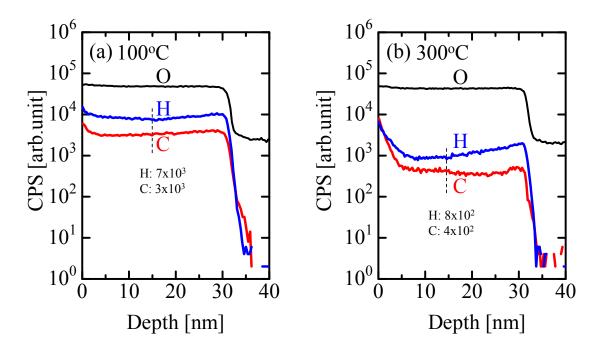

## 2.6.3 二次イオン質量分析 (SIMS) による ZnO 膜の組成評価

次に、堆積温度による ZnO 膜の組成の変化を調べるため、SIMS により ZnO 膜の元素分析を行った。100 におじ 300 で堆積した ZnO 膜の SIMS 測定の結果を図 2-21 (a)および(b)にそれぞれ示す。測定結果より、300 で堆積した ZnO では、100 で堆積した膜に比べて膜中の水素(H)および炭素(C)がおよそ 1 ケタ低減された

ことが示された。膜中の炭素および水素は、金属原料である DEZ に起因するものであると考えられる。本研究のこれまでの結果から、ZnO 膜中の残留炭素および水素の残留不純物が ZnO TFT における on 電流の低減につながると考えられるため、堆積温度の上昇による膜中の残留不純物の低減が、ZnO TFT 特性の向上の一因であると言える。

XRDによる結晶性評価及び SIMS による膜中元素分析の結果と、ZnO TFT における電気的特性とを比較して、ZnO 膜堆積温度の上昇による ZnO TFT 特性の向上は、結晶性の向上や膜中残留不純物の低減による ZnO 膜の高品質化に起因すると考えられる。

図 2-21. 堆積温度(a)100 $^{\circ}$ C、(b)300 $^{\circ}$ Cの ZnO 膜における SIMS 測定結果

## 2.6.4 可視光領域における透過率測定

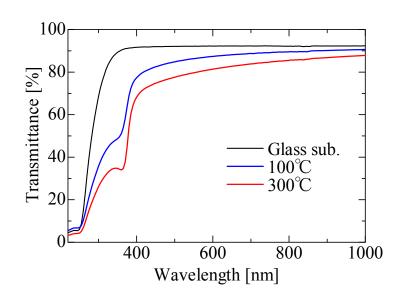

堆積温度に対する ZnO 膜の透明性の変化を調べるため、UV/VIS Spectrometer (Lambda 950)により可視光の透過率を測定した。200-1000 nm の波長に対する透過率の測定結果を図 2-22 に示す。堆積温度 100℃で形成した ZnO 膜では、可視光に対し最大で 90%以上の高い透明性を示し、波長 550 nm での透過率は約 86%であった。一方で、赤で示した 300℃で堆積した ZnO 膜では、100℃で堆積した膜を比較して透過率は低下し、550 nm の波長に対する透過率は約 80%であった。この堆積温度の上昇による透過率の低下は、電気的特性の測定結果と比較して、ZnO 膜中の酸素欠損の増加による欠陥準位の形成が原因として考えられる。34-36)しかしながら、いずれの堆積温度においても可視光に対し 80%以上の高い透過率を示しており、良好な透明性を持つ膜が形成されていると言える。

図 2-22 可視光透過率測定結果

# 2.7 ラジカル源による ZnO TFT の高性能化

## 2.7.1 水プラズマ ALD による ZnO 薄膜の形成

本研究のこれまでの結果から、ALD による ZnO TFT においては ZnO 膜中の残留炭素が on 電流や電界効果移動度の原因となることが分かった。さらに、ZnO 膜堆積温度への ZnO TFT 特性の依存性を評価した結果、 $300^{\circ}$ Cで堆積した ZnO 膜では c 軸優先配向を示し、高い電界効果移動度が得られた。これらの結果より、ZnO TFT 特性の向上には ZnO 膜中の残留炭素の低減および c 軸優先配向の膜の形成が重要である

ことが示された。一般的に、結晶性の向上や配向の制御のためには堆積温度または熱処理温度を上昇させる手段が用いられている。<sup>37-40)</sup> しかしながら、これらの高温プロセスは、プラスチック基板上等に形成するフレキシブルデバイスの作製に適用することは困難である。

そこで本節では、プロセス温度を上昇させることなく ZnO TFT の特性を向上させるため、PA-ALD による ZnO 膜形成時に使用するラジカル源の効果を検討した。通常の PA-ALD では、ラジカル源として酸素ガス( $O_2$ -plasma)を使用している。プラズマを印加しない酸素ガスでは、酸化剤としての反応性が非常に低く、原料ガスが酸化されないが、プラズマを印加することにより反応が活性化され低温でも原料ガスの酸化が可能となる。堆積温度の上昇による膜質の向上は、加熱による反応の活性化が行われているためと考えられることから、プラズマを使用しない通常の熱 ALD で使用される酸化剤にプラズマを印加することにより、 $O_2$ -plasma よりも高い反応のためのエネルギーが得られると考えた。そこで、従来の熱 ALD における酸化剤として一般的に使用される水をラジカル源として( $H_2O$ -plasma)使用した ZnO 膜を堆積し、ラジカル源による ZnO TFT 特性への影響を調べた。

$H_2O$ -plasma による ZnO TFT 特性への効果を調べるため、 $O_2$ -plasma により堆積した ZnO 膜を使用した TFT とその特性を比較した。また、ZnO 膜堆積時のプラズマ印加時間は  $0.1\sim1.5$  秒に変化させ、その特性の変化を調べた。膜の堆積温度は  $100^{\circ}$ とし、堆積した膜の膜厚は分光エリプソメトリにより測定した。さらに、ZnO 膜の特性を調べるため、XRD による結晶性の評価、AFM による表面形状の評価、SIMS による膜の深さ方向元素分析を行った。

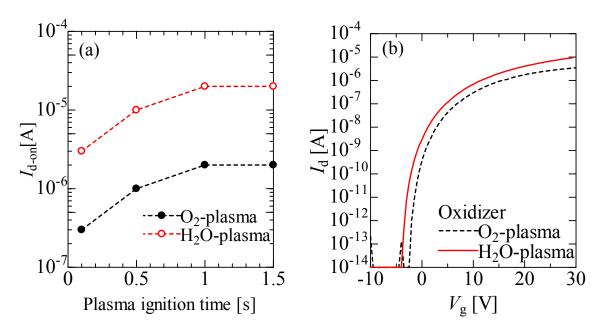

## 2.7.2 水プラズマ ALD による ZnO TFT 特性

熱酸化により  $SiO_2$  膜を形成した低抵抗 Si 基板上に、酸素ガスまたは水蒸気をラジカル源として使用した PA-ALD により ZnO 膜を堆積した。作製した TFT を  $V_d=5$  V における伝達特性を測定した。TFT 作製後の熱処理は行っていない。図 2-23 (a)に、プラズマ印加時間に対する on 電流の測定結果を示す。作製した TFT の on 電流は、 $O_2$ -plasma、 $H_2O$ -plasma 共にプラズマ印加時間の延長と共に増加し、約 1.0 秒のプラズマ印加時間で飽和する傾向がみられた。さらに、 $O_2$ -plasma による ZnO TFT と比較して、 $H_2O$ -plasma により堆積した ZnO 膜を使用した TFT では、短い印加時間でもより高い on 電流が得られた。図 2-23 (b)は、プラズマ印加時間 1.0 秒で堆積した ZnO 膜を使用した TFT の伝達特性を示している。プラズマ印加時間 1.0 秒での  $O_2$ -plasma および  $O_2$ -plasma  $O_3$   $O_3$   $O_4$   $O_4$   $O_5$   $O_5$   $O_5$   $O_6$   $O_6$   $O_7$   $O_8$   $O_8$   $O_9$   $O_9$

を示し、その on/off 比は 10<sup>9</sup>以上、閾値電圧は-0.5 V であった。

この結果は、現在ディスプレイの画素駆動用デバイスとして一般的に用いられている a-Si:H TFT の電界効果移動度( $\sim$ 0.5 cm²/Vs) よりも高い値を示しており、PA-ALD による ZnO TFT のディスプレイへの応用の可能性を示している。 $H_2O$ -plasma による ZnO TFT の特性向上の原因を調べるため、ZnO 膜の特性を評価した。

図 2-23.  $O_2$ -plasma および  $H_2O$ -plasma による ZnO TFT 伝達特性 (a)プラズマ印加時間に対する on 電流の変化 (b)プラズマ印加時間 1.0 秒で堆積した ZnO TFT 伝達特性 ( $V_d$ =5 V)

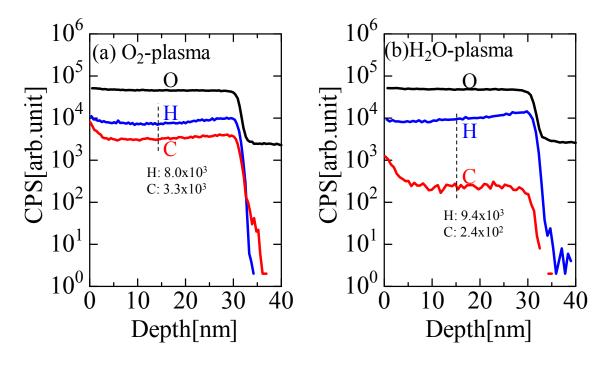

## 2.7.3 二次イオン質量分析による組成評価

本研究によるこれまでの結果から、ZnO 膜中の残留炭素が ZnO TFT の on 電流を低減することが明らかになっている。このことから、 $H_2O$ -plasma による ZnO TFT の on 電流および電界効果移動度の向上の原因を調べるため、 $H_2O$ -plasma および  $O_2$ -plasma により堆積された ZnO 膜の元素分析を行った。SIMS による元素分析の結果を図 2-24 に示す。 $H_2O$ -plasma により堆積した ZnO 膜では、 $O_2$ -plasma により堆積した膜に比べて、膜中の炭素が約 1 桁低減された。この炭素は、金属原料として使用した DEZ に起因する残留物質である。そのため、この膜中残留炭素の低減は、

$O_2$ -plasma と比較して  $H_2O$ -plasma の方が高い反応性を有するためであると考えられる。また、膜中の水素においてはラジカル源の変更による変化は見られなかったが、これはラジカル源として使用した  $H_2O$  から水素が取り込まれたためであり、DEZ に起因する残留水素は炭素と同様に低減されていると考えられる。この  $H_2O$ -plasma による ZnO 膜中の残留不純物の低減が、ZnO TFT の on 電流の向上につながったと考えられる。

図 2-23. (a)O<sub>2</sub>-plasma、(b)H<sub>2</sub>O-plasma による ZnO 膜の SIMS 測定結果

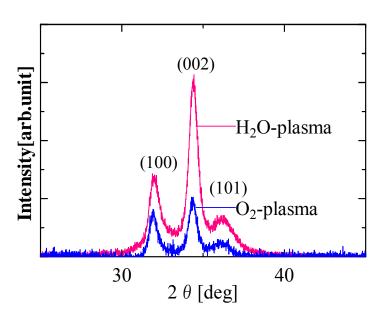

## 2.7.4 X 線回折による ZnO 膜の結晶性評価

本研究において ALD で堆積した ZnO 膜は、膜厚およそ 30 nm の多結晶薄膜である。ZnO TFT において、その特性は ZnO 膜の結晶性や表面モフォロジーからの影響を受ける。38 まず、ラジカル源の変化による ZnO 膜の結晶性の変化を調べるため、XRD 測定を行った。図 2-25 に ZnO TFT 作製に使用した ZnO 膜の XRD による測定結果を示した。 $O_2$ -plasma により堆積した ZnO 膜では、(100)、(002)、(101) の 3 つのピークがみられた。一方で、 $H_2O$ -plasma により堆積した ZnO 膜では、(100)、(101)のピークに対し、優勢な(002)のピークがみられた。この結果から、 $H_2O$ -plasma

により堆積したZnO膜では、基板に垂直なc軸優先配向の膜が得られている。このc軸優先配向により、ZnO 膜の粒界での欠陥準位が低減され、これにより ZnO TFT の 特性の向上につながったものであると考えられる。<sup>32-34)</sup> 一般的に、rf マグネトロン スパッタリングにより低温で堆積した ZnO 膜では、c 軸優先配向の膜が形成され、そ の配向はスパッタリングパワーや酸素ガスの流量比により制御される。39,41,42 また、 ALD により堆積した膜では、堆積温度の上昇により配向性が向上することが報告さ れている。40,41,43)本研究においても本章 6 節で示した通り、堆積温度の上昇により c軸配向の膜が得られることが示された。ALD による薄膜の堆積においては、堆積温 度の上昇により成膜の際の反応のためのエネルギーが増加することから、ZnO 膜の堆 積に使用するエネルギーがその配向に影響を与えると考えられる。このため、 O<sub>2</sub>-plasma と比較して H<sub>2</sub>O-plasma では堆積の際に温度が上昇している可能性が考 えられる。SIMS 測定の結果においても膜中の残留炭素が減少していることから、 H<sub>2</sub>O-plasma では O<sub>2</sub>-plasma と比較して反応が効果的に進んでいることがうかがえ る。以上のことから、ラジカル源として水を使用した H<sub>2</sub>O-plasma では、膜の堆積時 の反応が効果的に進むことにより、表面温度が上昇し、ZnO 膜の配向性が向上したの ではないかと考えられる。

図 2-25. O<sub>2</sub>-plasma および H<sub>2</sub>O-plasma による ZnO 膜の XRD 測定結果

## 2.7.5 AFM による ZnO 膜の表面形状評価

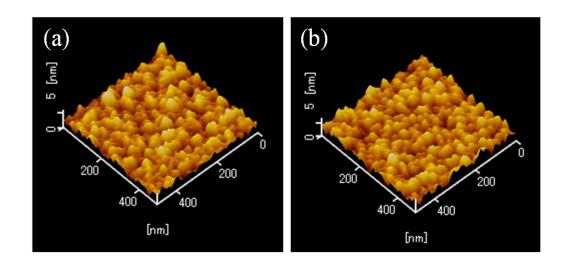

TFT において、チャンネル層の表面モフォロジーも特性に影響を与える。  $H_2O$ -plasma および  $O_2$ -plasma により堆積した ZnO 膜の表面モフォロジーを調べるため、AFM により任意の  $500\,$  nm ×  $500\,$  nm の領域を測定した。測定した ZnO 膜の表面モフォロジーの変化は、平均ラフネス $(R_a)$ により比較した。図 2-26 (a)および (b)に、プラズマ印加時間 1.0秒で堆積した  $O_2$ -plasma および  $H_2O$ -plasma による ZnO 膜の AFM-3D 画像を示す。 $O_2$ -plasma および  $H_2O$ -plasma による ZnO 膜の  $R_a$  は、共に約  $0.6\,$  nm であり、ラジカル源の変化による表面ラフネスの変化は見られなかった。また、多結晶 TFT において特性に影響を与えると考えられる、結晶粒の大きさについても、変化はないと推察される。

ZnO 膜の特性の測定結果から、 $H_2O$ -plasma による ZnO 膜の結晶性の向上は、膜中の残留炭素の低減によるものと考えられる。 XRD による結晶性の測定および SIMS による膜中元素分析の結果と、ZnO TFT の電気的特性の測定結果と比較して、 $H_2O$ -plasma により堆積した ZnO 膜を用いた TFT の特性の向上は、ラジカル源に水を使用したことで反応性の向上により ZnO 膜の膜質が向上したためであると考えられる。通常の ALD において ZnO 膜の膜質の向上のために必要であった、堆積温度の上昇による反応性の向上が、PA-ALD ではラジカル源の変更により得られた。この結果、PA-ALD により高品質な膜の低温での形成が可能となり、ZnO TFT の低温作製が可能となることが示された。

図 2-26. (a) O<sub>2</sub>-plasma、 (b) H<sub>2</sub>O-plasma による ZnO 膜の AFM-3D 画像

# 2.8 結言

本章では、原子層堆積法により ZnO 膜を堆積し、TFT 特性の向上のためのパラメータを検討した。まず、本研究の目的である ZnO TFT 作製プロセスの低温化に向けて、従来の熱 ALD 法と本研究で新たに提案した、反応の活性化にプラズマを印加する PA-ALD 法により低温で堆積した ZnO 膜をそれぞれ用いて TFT 特性を比較した。その結果、本研究で新たに提案した PA-ALD 法の ZnO 膜堆積への適用により、従来の手法による ZnO TFT で課題となっている高温での熱処理なしでスイッチング特性が得られた。さらに、熱 ALD と PA-ALD で堆積した ZnO 膜の特性を比較した結果、ZnO 膜中の残留炭素が ZnO TFT における電界効果移動度を低下させていることが分かった。

また、PA-ALDにより堆積した ZnO 膜を用いて作製した TFT の、熱処理による特性の変化を評価した結果、ZnO TFT の伝達特性は熱処理の温度の上昇と共に向上し、電気的ストレス下での不安定性も改善されることが分かった。この熱処理温度の上昇による伝達特性の向上は、ZnO 膜の結晶性の改善および膜中の酸素欠陥の補償がに起因し、さらに、電気的ストレス下での閾値電圧のシフトによる劣化は、ZnO 膜中の残留水素によるものであることが明らかとなった。

次に、PA-ALD による ZnO 膜の堆積時のパラメータについて検討した結果、TFT 特性はプラズマ印加時間の延長および堆積温度の上昇と共に向上することが分かった。ZnO 膜中の残留不純物も、プラズマ印加時間の延長および堆積温度の上昇と共に低減され、TFT 特性の向上を同じく ZnO 膜の膜質が改善されることが示された。さらに、300℃の高温で堆積した ZnO 膜では、c 軸優先配向の膜が得られた。可視光領域における透過率測定では、堆積温度 100℃で形成した ZnO 膜に対し、300℃で堆積した膜では透過率の低下がみられた。しかしながら、いずれの温度での堆積においても可視光に対し 80%以上の透過率を示したことから、良好な透明性を持つ膜が形成されていると考えられる。

これらの結果から、ZnO TFT の伝達特性の向上には、ZnO 膜中の残留炭素の低減および、結晶性の改善が重要であることが分かった。一般的に、これらの制御には堆積温度および熱処理温度の高温プロセスが用いられるが、プラスチック基板などのフレキシブル基板上へのデバイス形成が困難となる。そこで、プロセス温度を上げることなく、ZnO TFT の特性を向上させる手法として、PA-ALD による ZnO 膜堆積時のラジカル源の種類による TFT 特性への影響を調べた。その結果、ラジカル源に水を用いることにより、通常の酸素ガスをラジカル源とした ZnO 膜と比較して、堆積温度を上げることなく膜中の残留炭素を低減させることに成功した。さらに、この

$H_2O$ -plasma で堆積することにより、c 軸優先配向の膜が得られた。これにより、TFT 作製プロセスの温度を上昇させることなく、ZnO TFT が大きく改善された。

以上の結果から、本研究で提案した PA-ALD の適用により、ZnO TFT の高性能化が可能であることが示された。さらに、PA-ALD による ZnO 膜堆積条件の検討により、現在 ZnO TFT のフレキシブル基板上への作製において課題となっている、堆積温度、熱処理温度の低温化が可能となることがわかった。

# 参考文献

- <sup>1)</sup> Y. Kuo: Thin Film Transistors: *Materials and Processes* (Kluwer Academic, New York, 2004) Vol. 1, p. 6.

- <sup>2)</sup> T. Sameshima: *J. Non-Cryst. Solids*, **1196** (1998) 227.

- <sup>3)</sup> H. Kakinura: *Phys. Rev.*, **B 39** (1989) 10473.

- <sup>4)</sup> R. B. M. Cross, and M. M. D. Souza: *Appl. Phys. Lett.*, **89** (2006) 263513.

- <sup>5)</sup> Ü. Özgür, Y. I. Alivov, C. Liu, A. Teke, M. A. Reshchikov, S. Doğan, V. Avrutin, S. J. Cho, and H. Morkoç: *J. Appl. Phys.*, **98** (2005) 041301.

- <sup>6)</sup> P. F. Carcia, R. S. McLearn, M. H. Reilly, and G. Nunes: *Appl. Phys. Lett.*, **82** (2003) 1117.

- <sup>7)</sup> R. L. Hoffman, B. J. Norris, and J. F. Wager: *Appl. Phys. Lett.*, **82** (2003) 733.

- 8) S. Matsuda, K. Kitamura, Y. Okumura, and S. Miyatake: J. Appl. Phys., 93 (2003) 1624.

- <sup>9)</sup> E. Fortunato, P. Barquinha, A. Pimentel, A. Goncalves, A. Marques, L. Pereira, and R. Martins: *Thin Solid Films*, **487** (2005) 205.

- <sup>10)</sup> J. H. Chung, J. Y. Lee, H. S. Kim, N. W. Jang, and J. H. Kim: *Thin Solid Films*, **516** (2008) 5597.

- <sup>11)</sup> J.-J. Kim, J.-Y. Bak, J.-H. Lee, H. S. Kim, N.-W. Jang, Y. Yun, and W.-J. Lee: *Thin Solid Films*, **518** (2010) 3022.

- <sup>12)</sup> H.-Q. Huang, F.-J. Liu, J.-W. Zhao, Z.-F. Hu, Z.-J. Li, and X.-Q. Zhang: *J. Phys. and Chem. of Solids*, **72** (2011) 1393.

- <sup>13)</sup> K. Murata, K. Washio, N. Miyatake, Y. Mori, H. Tachibana, Y. Uraoka, and T. Fuyuki: *ECS Trans.*, **11**(7) (2007) 31.

- <sup>14)</sup> S. Kwon, S. Bang, S. Lee, S. Jeon, W. Jeong, H. Kim, S. C. Gong, H. J. Chang, H. Park, and H. Jeon: *Semicond. Sci. Technol.*, 24 (2009) 035015.

- <sup>15)</sup> D. H. Levy, D. Freeman, S. F. Nelson, P. J. Cowdery-Corvan, and L. M. Irving: *Appl. Phys. Lett.*, **92** (2008) 192101.

- <sup>16)</sup> S. J. Lim, S. J. Kwon, H. G. Kim, and J. S. Park: *Appl. Phys. Lett.*, **91** (2007) 183517.

- <sup>17)</sup> J. Jo, O. Seo, H. Choi, and B. Lee: *Appl. Phys. Express*, **1** (2008) 041202.

- <sup>18)</sup> 薄膜材料デバイス研究会編: *薄膜トランジスタ* 第2章, コロナ社, (2008).

- <sup>19)</sup> S. M. Sze: *Physics of Semiconductor Devices* 3<sup>rd</sup> *ed.*, Chapter 6, Wiley, New York, (2007).

- <sup>20)</sup> 岸野正剛: *半導体デバイスの物理*, 丸善株式会社, (1995).

- <sup>21)</sup> J. F. Moulder, W. F. Stickle, P. E. Sobol, and K. D. Bomben: *Handbook of X-ray*

- Photoelectron Spectroscopy, edited by J. Chastain, and R. C. King Jr. (Physical Electronics, Inc. publishers, Minnesota, 1995) 40.

- <sup>22)</sup> 八百隆文, ZnO 系の最新技術と応用, 株式会社 シーエムシー出版 (2007),

- <sup>23)</sup> Y. Uraoka, T. Hatayama, T. Fuyuki, T. Kawamura, and Y. Tsuchihashi: *Jpn. J. Appl. Phys.*, **39** (2000) L1209.

- <sup>24)</sup> A. R. Merticaru and A. J. Mouthaan: *Thin Solid Films*, **383** (2001) 122.

- <sup>25)</sup> M. J. Powell, C. van Berkel, and J. R. Hughes: *Appl. Phys. Lett.*, **54** (1989) 1323.

- <sup>26)</sup> F. R. Libsch and J. Kanicki: *Appl. Phys. Lett.*, **62** (1993) 1286.

- <sup>27)</sup> D.-H. Cho, S.-H. K. Park, S. Yang, C. Byun, S. M. Chung, W.-S. Cheong, J. Shin, M. K. Ryu, J. I. Lee, C.-S. Hwang, S. M. Yoon, H.-Y. Chu, and K. I. Cho: *IDW'09 Dig. 2008*, p.1625.

- <sup>28)</sup> K. K. Shin, and D. B. Dove: *J. Vac. Sci. Technol.*, A **12** (1994) 321.

- <sup>29)</sup> R. G. Frieser: *J. Electrochem. Soc.*, **113** (1966) 357.

- <sup>30)</sup> N. Hattori, K. Murata, N. Miyatake, Y. Kawamura, and Y. Uraoka: *Proc. 16th Int. Display Workshops*, (2009) FMC1-3.

- <sup>31)</sup> Y. Zhang, and J. Han: *Mater. Lett.*, **60** (2006) 2522.

- <sup>32)</sup> L. Gao, Q. Li, and W. Luan: J. Am. Ceram. Soc., **85** (2002) 1016.

- <sup>33)</sup> K. Kakinuma, K. Kanda, and H. Yamada: *J. Mater. Sci.*, **37** (2002) 7.

- <sup>34)</sup> D. Raoufi, and T. Raoufi: *Appl. Surf. Sci.*, **255** (2009) 5812.

- <sup>35)</sup> J. Tauc, R. Grigorovichi, and A. Vancu: *Phys. Status Solidi*, **15** (1966) 627.

- <sup>36)</sup> C.-Y. Tsay, K.-S. Fan, S.-H. Chen, and C.-H. Tsai: *J. Alloys Comp.*, **495** (2010) 126.

- <sup>37)</sup> H.-Q. Huang, F.-J. Liu, J.-W. Zhao, Z.-F. Hu, Z.-J. Li, and X.-Q. Zhang: *J. Phys. and Chem. of Solids*, **72** (2011) 1393.

- <sup>38)</sup> L. Zhang, H. Zhang, Y. Bai, J. W. Ma, J. Cao, X. Y. Jiang, and Z. L. Zhang: *Solid State Commun.*, **146** (2008) 387.

- <sup>39)</sup> S. J. Lim, S. Kwon, and H. Kim: *Thin Solid Films*, **516** (2008) 1523.

- <sup>40)</sup> J. Malm, E. Sahramo, J. Perala, T. Sajavaara, and M. Karppinen: *Thin Solid Films*, **519** (2011) 5319.

- <sup>41)</sup> E. M. C. Fortunato, P. M. C. Barquinha, A. C. M. B. G. Pimentel, A. M. F. Gonçalves, A. J. S. Marques, L. M. N. Pereira, and R. F. P. Martins: *Adv. Matter.*, **17** (2005) 590.

- <sup>42)</sup> W.-S. Cheong, M.-K. Ryu, J.-H. Shin, S.-H. K. Park, and C.-S. Hwang: *Thin Solid Films*, **516** (2008) 8159.

- <sup>43)</sup> A. Wojcik, M. Godlewski, E. Guziewicz, R. Minikayev, and W. Paszkowicz: *J. Crystal Growth*, **310** (2008) 284.

# 第3章 ZnO TFT における ALD による絶縁膜の効果

# 3.1 緒言

近年、ALD により形成された薄膜の様々なアプリケーションへの適用が検討されている。表 3-1 に ALD 膜のアプリケーションの一部を示した。この中でも代表的なアプリケーションはキャパシタ、磁気ヘッド、ゲート絶縁膜などの high-k 膜であり、一部実用化が始まっている。これらのアプリケーションを見ると、薄膜での膜厚制御性、段差被覆性、緻密性などの特徴を生かしたものが多い。また、材料から見ると  $Al_2O_3$  膜の適用が多いことが分かる。これは  $Al_2O_3$  膜の良好な物性によるところもあるが、原料であるトリメチルアルミニウム( TMA: Trimethyl aluminum,  $Al(CH_3)_3$ ) の取り扱いが比較的容易であり、ALD プロセスが成熟していることも影響している。

| アプリケーション         | 材料                                                                                                                                     |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| ゲート絶縁膜(high-k)   | HfO <sub>2</sub> , Al <sub>2</sub> O <sub>3</sub> , Ta <sub>2</sub> O <sub>5</sub> , ZrO <sub>2</sub> , La <sub>2</sub> O <sub>3</sub> |

| キャパシタ            | HfO <sub>2</sub> , Al <sub>2</sub> O <sub>3</sub> , Ta <sub>2</sub> O <sub>5</sub>                                                     |

| 保護膜(EL 素子など)     | $Al_2O_3$                                                                                                                              |

| パッシベーション(太陽電池など) | $Al_2O_3$                                                                                                                              |

| ゲート電極            | Pt, Cu, Ni, Al                                                                                                                         |

| バリアメタル           | TiN                                                                                                                                    |

| 酸化物半導体           | ZnO, In <sub>2</sub> O <sub>3</sub>                                                                                                    |

表 3-1 ALD 膜のアプリケーション 1-3)

ALD 膜は現状ではウエハサイズのデバイスに適用されることが多い。しかしながら、CVD などに比べて低温での成膜が可能なことや、均一に成膜可能なことから、ディスプレイなどの大面積への成膜にも適していると考えられる。現状においては、大面積への適用例は少ないが、これまでに  $Al_2O_3$  膜などにおいて大面積への成膜が可能であることが報告されている。 $^{4)}$  これらの ALD 膜の特徴が、酸化物半導体TFT においても有効であると考えられる。

本研究では、ALD により堆積した ZnO 薄膜の特性および TFT への応用について研究してきた。ALD により堆積された ZnO 膜において、現在課題とされている膜中の過剰残留キャリア を制御する手法として、酸化剤にプラズマを印加した活性酸素を使用する PA-ALD 法を提案し、その有用性を検討してきた。ZnO 膜の堆積時の

プラズマの有無、および堆積後の熱処理前後での ZnO 膜の物性及び電気的特性を測定した。その結果、PA-ALD により堆積した ZnO 膜を使用した ZnO TFT では、第2章で示した通り、通常の熱 ALD による ZnO 膜を使用した TFT に比べ、低温でも非常に優れた特性が得られた。これまでの結果から、PA-ALD 法により ZnO 膜中の残留キャリア濃度が低減され、高性能 ZnO TFT の低温での作製が可能となることを示してきた。

本章では、PA-ALDにより堆積した ZnO 膜を使用する TFT の更なる特性向上に向け、ALDにより堆積したアルミナ膜の効果を検討した。アルミナは、素子の小型化に伴う絶縁膜の薄膜化や、駆動電圧の低減に対応するための絶縁膜材料として近年検討されている High-k 材料の一種である。さらに本研究で使用する ALD 堆積装置では、使用する金属原料を変更することにより、In-situでの連続成膜が可能となる。このため、絶縁膜/ZnO 膜界面が汚染されず良好な界面状態を得られることから、膜質の向上が期待できる。 ZnO TFT のゲート絶縁膜として ALD によりアルミナ膜を堆積し、アルミナ膜の堆積条件の変化による、ZnO TFT の特性への影響を調べた。また、酸化亜鉛系 TFT において、バイアスストレス下での不安定性には、大気中の水分が影響することが知られている。このことから、パッシベーション膜による ZnO チャネル層の封止が信頼性の向上につながると考えられるため、作製した ZnO TFT 上に ALDによりアルミナ膜を堆積し、信頼性の向上への効果を調べた。

# 3.2 ALD 法による絶縁膜の形成および ZnO TFT 特性への効果

## 3.2.1 ALD 法による絶縁膜の形成

現在、ディスプレイ駆動素子として一般的に使用されている a-Si:H TFT のゲート絶縁膜には、PE-CVD 等により  $400^{\circ}$ C程度の高温で堆積された  $SiO_2$  膜が使用されている。本研究では、次世代ディスプレイへの応用に向け、ZnO TFT のチャネル層である ZnO 膜の形成に PA-ALD 法を適用することで、チャネル層の形成温度の低温化および TFT 特性の向上が可能であることを明らかにしてきた。しかしながら、次世代ディスプレイへの適用に必要とされる、フレキシブル基板上への素子形成には、この絶縁膜の堆積温度も低減される必要がある。そこで本研究では、低温でも緻密な膜の形成が可能であることから、ALD により絶縁膜としてアルミナ膜を形成し、ZnO TFT の絶縁膜への適用を検討した。

アルミナ膜成膜のための金属原料として TMA、パージガスとして  $N_2$  ガスを用いた。従来の熱 ALD 法による堆積では、酸化剤として  $O_3$   $(O_3-ALD)$  を使用した。さらに、ZnO 膜の低温形成において PA-ALD 法の適用により高品質化の可能性が示さ

れたことから、PA-ALD によりアルミナ膜を堆積し、従来法との特性を比較した。また、PA-ALD 法による堆積時の条件の変化による特性の変化を調べるため、プラズマ 印加時間を 0.1-1.0s と変化させた。フレキシブル基板上への作製に向けた ZnO TFT の 低温プロセス化の為、アルミナ膜の堆積温度は 100 Cとした。

## 3.2.2 ALD による絶縁膜の特性評価

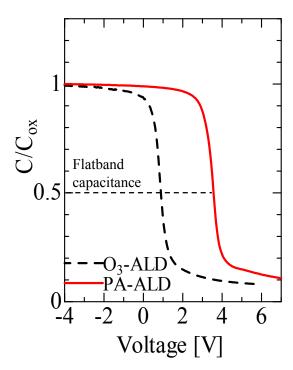

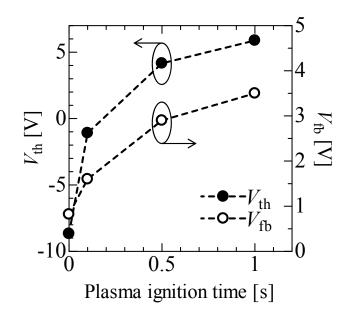

PA-ALD により堆積したアルミナ膜の電気的特性を調べるため、金属 - 酸化膜 - 半導体(MOS)キャパシタを作製し、容量-電圧(C-V)測定を用いてアルミナ膜のフラットバンド電圧( $V_{tb}$ )を計算した。 MOS キャパシタは、p-type Si(100)基板上に O<sub>3</sub>-ALD および PA-ALD によりアルミナ膜を堆積し、窒素雰囲気中で 300℃、30分の熱処理を行った。図 3-1 に C-V 測定の結果を示す。黒の破線は、O<sub>3</sub>-ALD によるアルミナおよび赤の実線でプラズマを 1.0 秒印加した PA-ALD によるアルミナの C-V 曲線を示している。C-V 曲線はプラズマ印加時間の延長と共に正方向へとシフトし、1.0 秒印加した膜では、 $V_{tb}$ は約 4.2 V であった。この結果を基に、膜中に均一に電荷が存在すると仮定した場合、膜中の電荷密度はおよそ 4x10<sup>17</sup> cm<sup>-3</sup> と見積もられる。これは、膜中の酸素または残留不純物である炭素に起因する欠陥によるものであると考えられる。

図 3-1 ALD によるアルミナ膜を使用した MOS キャパ シタの C-V 特性

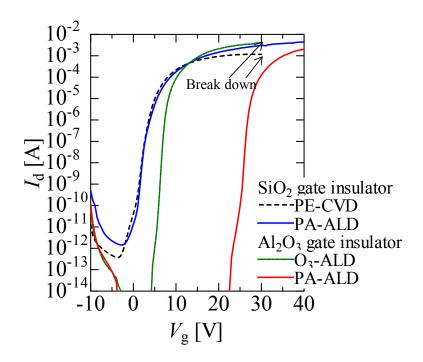

### 3.2.3 ALD によるゲート絶縁膜を用いた ZnO TFT 特性

第2章6節において ZnO 膜堆積温度に対する ZnO TFT 特性の依存性を調べた結果、300℃で堆積した ZnO 膜をチャネル層として使用した TFT では、100℃で堆積したものに対し高い電界効果移動度が得られた。しかしながら、100℃で堆積した ZnO TFT では約 $0.6\,V$  であった閾値電圧が、300℃で堆積した ZnO TFT では- $16.0\,V$  と負側への大きなシフトがみられた。ZnO TFT の伝達特性において、閾値電圧の負側へのシフトは ZnO 膜中の酸素欠損の増加に起因し、また ZnO 膜は酸素欠損が生成されやすい材料であることが知られている。50

一方で、ALD 法により堆積したアルミナ膜は、フラットバンド電圧が正側へとシフトする傾向を持つことが報告されている。<sup>6,7)</sup> 本研究においても、従来の熱 ALD および本研究で提案する PA-ALD により堆積したアルミナ膜では、いずれもそのフラットバンド電圧は正の値を示した。このため、ALD により堆積したアルミナ膜を ZnO TFT のゲート絶縁膜として使用することにより、ZnO TFT の閾値電圧の負側へのシフトを抑制できることが期待される。

そこで、 $O_3$ -ALD および PA-ALD によりアルミナ膜を 100  $^{\circ}$   $^{\circ}$  で堆積した低抵抗 Si 基板上に、チャネル層として ZnO 膜を PA-ALD により堆積し、ZnO TFT を作製した。 ZnO 膜の堆積温度は 300  $^{\circ}$   $^{\circ}$  とし、プラズマ印加時間は 1.0s とし、アルミナ膜堆積時のプラズマ印加時間を  $0(O_3$ -ALD)から 1.0s と変化させた時の、ZnO TFT 特性の変化を調べた。

作製した  $Z_{nO}$  TFT の伝達特性の測定結果を、図 3-2 に示す。従来のプラズマを印加しない  $O_3$ -ALD によるアルミナ膜をゲート絶縁膜として使用した TFT では、閾値電圧は約-9.0 V であり、熱酸化膜を使用した TFT の-16 V と比較すると閾値のシフトは改善された。しかしながら、スイッチング素子としてはゲート電圧 0 V でオフのノーマリー・オフが望ましいため、更なる正側への改善が必要である。この閾値の負側へのシフトが、PA-ALD で堆積したアルミナ膜を使用した  $Z_{nO}$  TFT では大きく改善され、プラズマ印加時間 0.5 秒以上のものではノーマリー・オフの特性が得られた。

図 3-3 に、作製した  $Z_{nO}$  TFT の閾値電圧と、ゲート絶縁膜として使用したアルミナを用いて作製した MOS キャパシタのフラットバンド電圧の、プラズマ印加時間に対する変化を示した。TFT の  $V_{th}$  および MOS キャパシタの  $V_{fb}$  は共に、プラズマ印加時間の延長と共に正側へとシフトした。このことから、アルミナ膜堆積時のプラズマ印加時間の延長による  $Z_{nO}$  TFT の閾値電圧の正側へのシフトは、ゲート絶縁膜であるアルミナ膜の電気的特性の変化に起因するものであることが示唆された。

ALD 法により堆積したアルミナ膜をゲート絶縁膜として使用し、ZnO TFT 特性への効果を調べた。その結果、プラズマを印加しない  $O_3$ -ALD および、プラズマ印

加時間 0.1s の PA-ALD で堆積したアルミナ膜を使用した TFT では、 $V_g=0$  V でオン状態のデプレション型の特性を示した。一方で、プラズマ印加時間 0.5 s 以上の PA-ALD により堆積したアルミナ膜を使用したものでは、 $V_g=0$  V でオフ状態のエンハンスメント型の TFT が得られた。以上の結果から、堆積条件の検討によりゲート絶縁膜の特性を制御することで、ZnO TFT の閾値の制御が可能となることが示された。

図 3-2 ZnO TFT 伝達特性 (V<sub>d</sub>=5 V)

図3-3 プラズマ印加時間に対する ZnO TFT の閾値電圧 および MOS キャパシタのフラットバンド電圧の変化

# 3.3 ALD によるゲート絶縁膜を用いた低温プロセス ZnO TFT の特性向上

## 3.3.1 ALD による ZnO TFT 低温作製

これまでの結果から、PA-ALD により堆積したアルミナ膜をゲート絶縁膜として使用することで、 $V_g$ =0 V でオフ状態が得られ、off 電流が低減されることが分かった。一方で、従来の熱 ALD により堆積したアルミナを使用した ZnO TFT では、図 3-2 に示すようにオン領域において高い on 電流が得られた。そこで本実験では、ZnO TFT 特性の向上に向け、高い on 電流と off 電流の低減を得るために、PA-ALD により膜厚 45 nm のアルミナ膜を堆積した上に 5 nm のアルミナを  $O_3$ -ALD により堆積し、積層アルミナ膜をゲート絶縁膜として形成し、その TFT 特性への効果を検討した。比較として、熱酸化による  $SiO_2$  膜および PA-ALD による単層のアルミナ膜を用いた ZnO TFT を作製し、特性を評価した。ZnO 膜およびアルミナ膜の堆積温度は 100 とし、PA-ALD におけるプラズマ印加時間は 1.0 s とした。

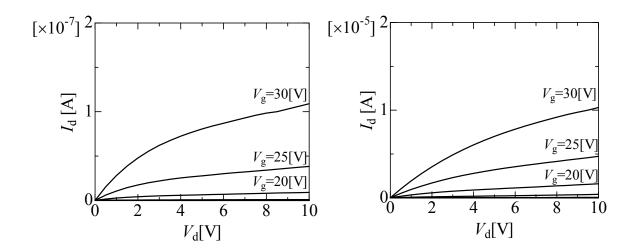

作製した  $Z_{nO}$  TFT の、 $V_{n=5}$  V における伝達特性および出力特性の測定結果を 図 3-4 に示す。 全ての TFT で、良好なスイッチング特性が得られ、アルミナ膜をゲ ート絶縁膜と使用したものでは、熱酸化膜を使用したものと比較して高い電界効果移 動度が得られた。さらに、PA-/O3-ALD の積層アルミナ膜をゲート絶縁膜とした TFT では、PA-ALD 単層のアルミナ膜を使用したものよりも特性の向上がみられた。図 3-4(d)および(e)は、熱酸化膜および積層アルミナ膜をゲート絶縁膜として使用した TFT の出力特性を示している。いずれの TFT においても、飽和領域の  $V_{tt}$  において  $I_{tt}$ が増加するキンク電流は見られず、良好な出力特性が得られている。また、積層アル ミナ膜を使用した TFT では、熱酸化膜を使用した TFT と比較して高い電流値を示し た。この結果、積層アルミナゲート絶縁膜の ZnO TFT では、 $10^9$ 以上の on/off 比が得 られ、電界効果移動度は  $5.1~\mathrm{cm^2V^{-1}s^{-1}}$ 、S 値は  $0.2~\mathrm{V/decade}$  であった。熱酸化膜およ び PA-ALD 単層アルミナ膜をゲート絶縁膜とした ZnO TFT の電界効果移動度は、そ れぞれ 1.0 および 1.6 cm $^2$ V $^{-1}$ s $^{-1}$ であった。ZnO TFT の S 値および電界効果移動度は、 界面準位密度やトラップ等、TFT 駆動時にチャネル領域となる ZnO/ゲート絶縁膜界 面の状態による影響を大きく受ける。このため、ゲート絶縁膜の変更による TFT 特性 の向上は、ZnO チャネル膜とゲート絶縁膜の界面状態の改善による可能性が考えられ る。

図 3-4 (a)熱酸化膜、(b)PA-ALD 単層アルミナ膜、(c)PA-/O<sub>3</sub>-ALD 積層アルミナ膜をゲート絶縁膜とした ZnO TFT の伝達特性( $V_d$ =5 V)。 (d) 熱酸化膜、(e) PA-/O<sub>3</sub>-ALD 積層アルミナ膜をゲート絶縁膜とした ZnO TFT の出力特性

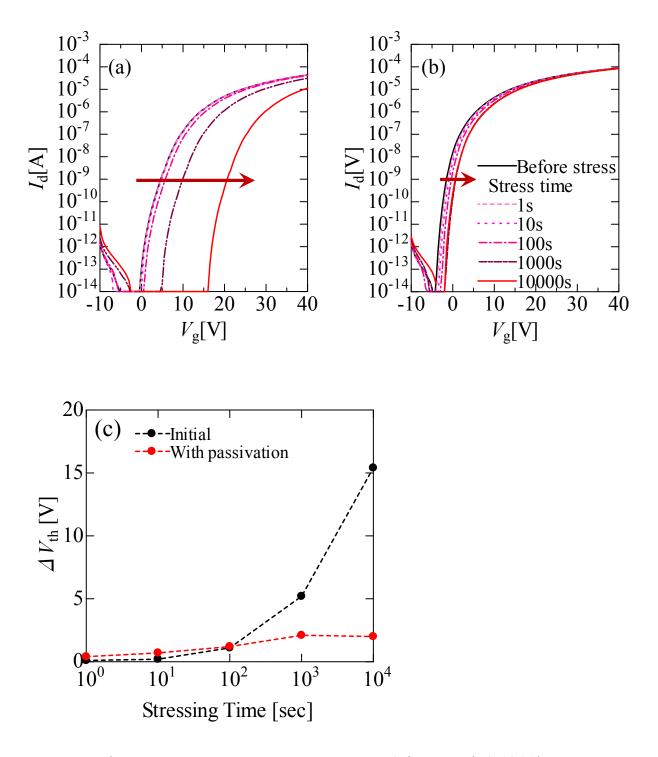

## 3.3.2 ALD による ZnO TFT の電気的ストレス下における信頼性評価

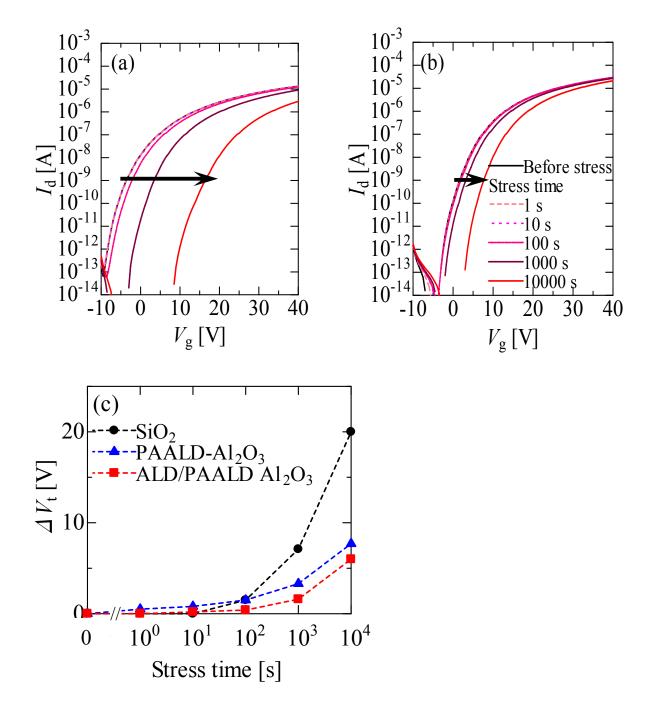

TFT のゲートバイアスストレス下での安定性には、ZnO/ゲート絶縁膜界面の 状態が影響することが報告されている。<sup>8,9)</sup> そこで、作製したそれぞれの ZnO TFT の、ゲート絶縁膜の変更による電気的ストレス印加時の安定性への影響を調べた。ゲ ートバイアスとして 20 V を印加し、ゲートバイアスストレス下での信頼性評価を行 った。図 3-5 (a)および(b)は、それぞれゲート絶縁膜に熱酸化膜および積層アルミナ膜 を使用した ZnO TFT の、バイアスストレス下での伝達特性の変化を示している。熱酸化膜を使用した ZnO TFT では、10000 秒のストレス印加により、閾値電圧が大きく正側へとシフトした。このストレス印加によるシフトが、積層アルミナ膜を使用したTFT では大きく低減された。図 3-5 (c)に、ゲートバイアスストレス下での、時間経過による閾値のシフト量の変化を示した。10000 秒のゲートバイアスストレス印加後、熱酸化膜をゲート絶縁膜とした ZnO TFT では約 20 V であった閾値のシフトが、ALD により堆積したアルミナを使用したものでは 10 V 以下に低減され、さらに、積層アルミナ膜をゲート絶縁膜とした TFT では、閾値のシフトが約 6 V と単層のものよりもそのシフトが改善した。

PA-/O<sub>3</sub>-ALD 積層アルミナ膜をゲート絶縁膜として使用した ZnO TFT の伝達特性の測定結果から、熱酸化膜を使用した ZnO TFT と比較して S 値の改善がみられた。TFT の S 値およびゲートバイアスストレス下で安定性は、共に ZnO/ゲート絶縁膜界面の状態が影響を及ぼすことが報告されている。 $^{8-10)}$  このことから、ゲート絶縁膜の変更によるバイアスストレス下での安定性の向上は、ZnO/ゲート絶縁膜界面の状態が変化し、信頼性の向上に寄与した可能性が考えられる。

図 3-5 ゲートバイアス 20V 印加による信頼性評価 (a)熱酸化膜、(b)積層アルミナ膜をゲート絶縁膜とした ZnO TFT のバイアスストレス印加による伝達特性の変化、(c)ゲートバイアスストレス下での時間経過による閾値電圧の変化量の推移

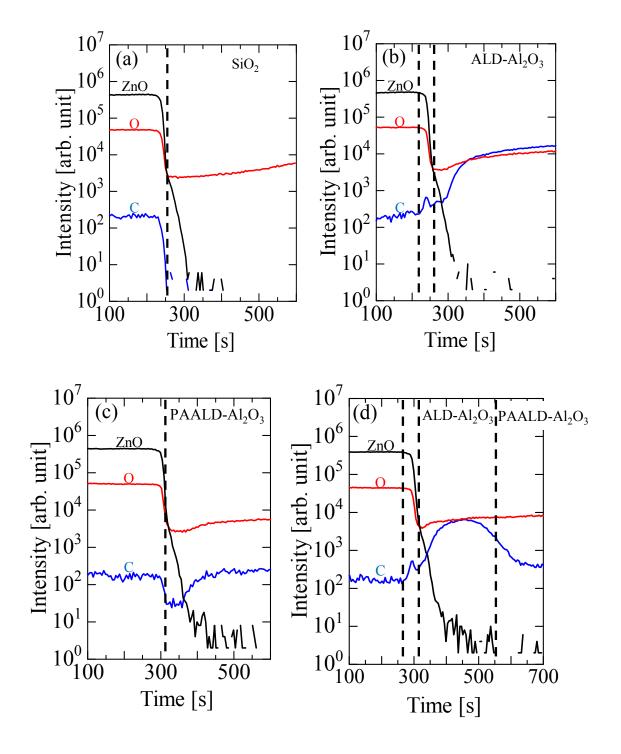

### 3.3.3 SIMS による深さ方向の組成測定

ゲート絶縁膜の変更による ZnO/ゲート絶縁膜界面の変化を調べるため、SIMS 測定による深さ方向の元素分布分析を行った。図 3-6(a)-(d) に、ZnO 膜およびゲート 絶縁膜の界面付近の測定結果を示す。図 3-6(b) に示した従来の ALD により堆積した アルミナ膜と比較して、図 3-6(c) に示した PA-ALD により堆積したアルミナ膜では、 膜中の炭素が約2ケタと大きく減少した。この炭素の減少は、プラズマの印加により 金属原料に起因する残留不純物が低減されたことを示唆している。さらに、図 3-6 (b) および(c) に示した熱 ALD 単層アルミナおよび積層アルミナ膜上に堆積した ZnO 膜 の試料では、ZnO/ゲート絶縁膜界面付近の ZnO 膜において、炭素の増加がみられた。 この傾向は、図 3-6(a)および(d) に示した熱酸化膜および PA-ALD 単層アルミナ上の、 界面に熱 ALD によるアルミナ層がない試料の界面では見られなかった。これらの結 果から、界面付近における ZnO 膜中の炭素の増加は、熱 ALD によるアルミナ膜中の 残留炭素に由来するものであると考えられ、ZnO/ALD アルミナ界面において界面層 が形成されていることを示唆していると考えられる。この界面層には、ZnO だけでな くアルミ原子も含んでいる。この界面層でのアルミ原子がキャリアとして振る舞い、 結果として TFT においてチャネルを形成するゲート絶縁膜との界面付近においてキ ャリア濃度が増加し、低抵抗層が形成されたことで  $I_{don}$  の増加及び移動度の向上につ ながったと考えられる。

これら SIMS 測定から得られた結果と、ZnO TFT の伝達特性の測定結果を比較して、ZnO/ゲート絶縁膜界面に界面層が形成されたことで、ZnO/ゲート絶縁膜界面において、良好な界面状態が得られたと考えられる。これにより、S値の改善にみられる界面準位密度の低減等が生じ、ZnO TFT のデバイス特性の向上につながったと考えられる。

図 3-6 SIMS 測定結果 (a)熱酸化膜、(b)熱 ALD による単層アルミナ膜、(c)PA-ALD による単層アルミナ膜、(d)熱 ALD / PA-ALD 積層アルミナ膜上 ZnO 膜

## 3.3.4 ALD による酸化亜鉛薄膜の高機能化に向けた検討

ALD による TCO の堆積では、ZnO 膜の堆積において ZnO 膜数十サイクルに対しアルミナ膜を 1 層挟み込むといったサンドイッチ構造が検討され、抵抗率の低減が報告されている。 $^{20)}$  本研究においても、ZnO/アルミナ膜の積層により、低抵抗な界面層が形成されることが示唆された。ZnO 系の TFT において、チャネルとなるゲート絶縁膜との界面に低抵抗層を形成することで、特性が向上するという報告もされている。 $^{21)}$  本節で示した、PA-/熱 ALD による積層ゲート絶縁膜による ZnO TFT 特性の向上も、この界面付近での低抵抗層の形成が一因となっていることが考えられる。

そこで、ALD による ZnO 膜の高機能化に向け、ZnO 膜の堆積過程でアルミナ膜の金属原料である TMA を投入し、ZnO 膜の抵抗率の低減を試みた。成膜におけるタイムチャートを図 3-7 に示す。堆積温度は太陽電池のパッシベーション用途に使用されるアルミナ膜の標準的な堆積温度である 250 とし、プラズマを印加しない従来の熱 ALD により堆積を行った。ZnO 膜の成膜サイクル中に投入する TMA の量を DEZ の量に対し体積比で  $0\sim2.5\%$ と変化させ、堆積した膜の電気的特性を評価するためホール効果測定を行った。さらに、酸素欠損を増加させることによる抵抗値の低減を図るため、水素雰囲気( $H_2=10$  %,  $N_2=90$  %)中で熱処理を行い、抵抗率の変化を調べた。

堆積した膜の測定結果を、表 3-2 に示す。その結果、TMA を投入しない ZnO 膜と比較して TMA を投入した ZnO 膜ではキャリア濃度が増加し、膜の比抵抗値が 1 桁低減された。この膜を水素雰囲気中で熱処理することにより比抵抗値はさらに低下し、 $10^{-2}$   $\Omega$ cm と言う低い比抵抗値を示した。現在電極用途で使用されている一般的な透明導電膜の比抵抗値は  $10^{-3}$   $\Omega$ cm 程度であることから、更なる低抵抗化が必要である。しかしながら、本結果は ZnO 膜を ALD 法で堆積することにより、半導体とし

てだけではなく、透明導電膜としても使用できる高機能な膜の形成が可能となること を示唆している。

図 3-7 ALD 法による Al ドープ ZnO 膜堆積タイムチャート

表 3-2 Hall 効果測定結果

| TMA 投入量 | キャリア濃度              | 比抵抗                 | 熱処理後比抵抗              |

|---------|---------------------|---------------------|----------------------|

| [%]     | [/cm <sup>3</sup> ] | $[\Omega cm]$       | $[\Omega cm]$        |

| 0       | $1.1x10^{17}$       | $5.9x10^{1}$        |                      |

| 1.0     | $4.8x10^{17}$       | $7.5 \times 10^{0}$ | 4.1x10 <sup>-2</sup> |

| 1.5     | $2.4x10^{18}$       | $3.1x10^{0}$        | $2.3 \times 10^{-2}$ |

| 2.5     | $2.5x10^{18}$       | $1.3x10^{0}$        | 3.1x10 <sup>-2</sup> |

# 3.4 ALD による低温プロセス ZnO TFT へのパッシベーション

# 膜の効果

## 3.4.1 ZnO TFT 上パッシベーション膜の形成

酸化亜鉛系材料は、ガスセンサー等にも使用される材料であり、その電気的特性は雰囲気により影響を受けると考えられる。酸化亜鉛系 TFT へのバイアスストレス印加時において、大気中の酸素および水分等が ZnO チャネル層表面に吸着し、閾値のシフトといった特性劣化の要因となることが近年報告されている。<sup>21,22)</sup>そのため、ZnO TFT の信頼性向上には、チャネル層を大気雰囲気から保護するためのパッシベーション膜の形成が不可欠である。<sup>23-26)</sup> ZnO TFT のパッシベーション膜には、大気中の水分等を防止するため、膜の緻密性が重要となる。そこで、ZnO TFT のパッシベーション膜として、有機 EL ディスプレイの水分封止膜等としても一部で実用が検討されており、低温でも緻密な膜の形成が可能である ALD によるアルミナ膜を使用し、その効果を検討した。

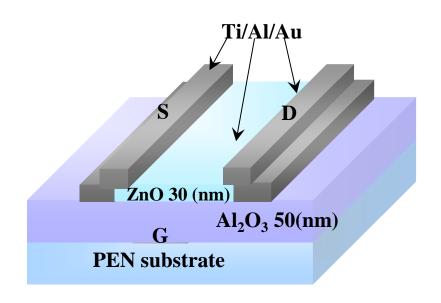

低抵抗 Si 基板上にゲート絶縁膜として PA-ALD によりアルミナ膜 50 nm を堆積した後、ZnO 膜 30 nm を堆積し、ウェットエッチングによりパターニングを行った。 Ti/Al/Au を積層し、リフトオフプロセスにより S/D 電極を形成し作製したボトムゲート型 ZnO TFT 上に、ALD によりパッシベーション膜としてアルミナ膜 50 nm を堆積し、ウェットエッチングによりコンタクトホールを形成した。 TFT の断面図を図 3-8 に示す。パッシベーション膜の形成には、通常の熱 ALD( $O_3$ -ALD)および PA-ALDを使用して特性を比較した。アルミナ膜および ZnO 膜の堆積温度は 100 Cとし、堆積後および TFT 作製後の熱処理は行っていない。

図 3-8 パッシベーション膜付 Bottom-gate-type ZnO TFT 断面図

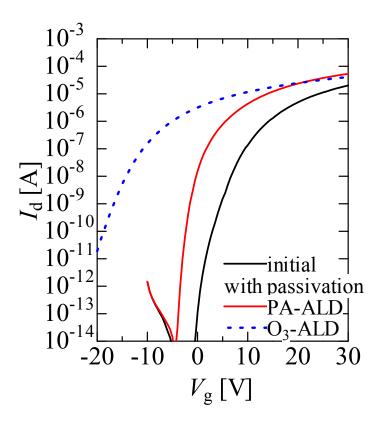

## 3.4.2 ZnO TFT 特性へのパッシベーション膜の効果

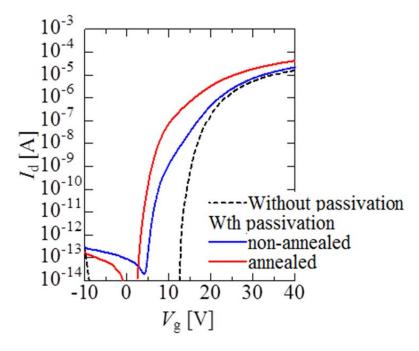

ZnO TFT 作製後の、パッシベーション膜形成前後での伝達特性を測定した。ドレイン電圧に 5V を印加した時の、伝達特性の測定結果を図 3-9 に示す。 $O_3$ -ALD によるアルミナ膜をパッシベーション膜として使用した TFT では、閾値電圧が約-16.6 V と、大きく負側へとシフトした。ZnO TFT における閾値電圧の負側へのシフトは、ZnO 膜中の酸素欠陥に起因することが知られている。 $O_3$ -ALD により低温形成したアルミナ膜では、本章 3 節に示した SIMS 測定の結果から、PA-ALD による膜よりも膜中の残留炭素が約 1 桁多いことが分かっている。このことから、金属原料である TMA の酸化が不十分であり、チャネル層である ZnO 膜からパッシベーション膜であるアルミナ膜への酸素の吸着が起こり、ZnO 膜中の酸素欠陥が増加した結果、閾値電圧の負側へのシフトが発生したと考えられる。

図 3-9 パッシベーション膜形成前後での ZnO TFT 伝 達特性の変化 ( $V_d=5$  V)

表 3-3 ZnO TFT 特性

|                       | Initial | With passivation    |        |

|-----------------------|---------|---------------------|--------|

|                       |         | O <sub>3</sub> -ALD | PA-ALD |

| 電界効果移動度               | 2.6     | 2.5                 | 3.0    |

| [cm <sup>2</sup> /Vs] |         |                     |        |

| 閾値電圧                  | 5.0     | -16.6               | -1.0   |

| [V]                   |         |                     |        |

| S値                    | 0.56    | 0.50                | 0.28   |

| [V/decade]            |         |                     |        |

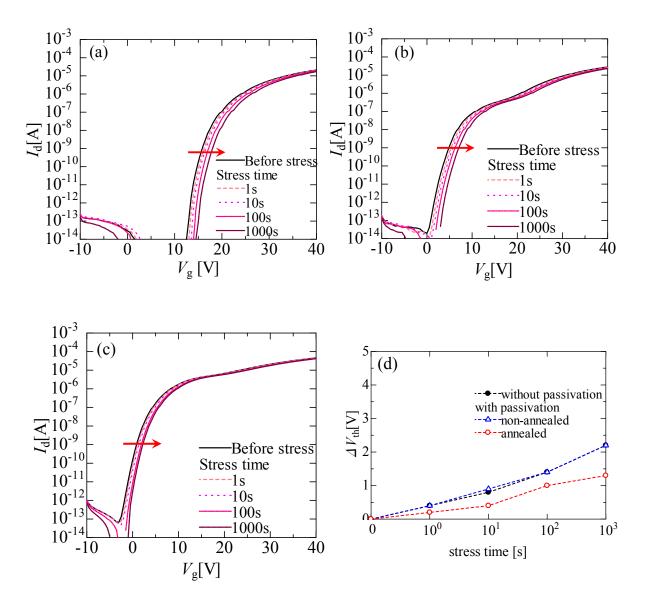

#### 3.4.3 PA-ALD パッシベーション膜による ZnO TFT の信頼性の改善

PA-ALD により堆積したパッシベーション膜の、ZnO TFT のバイアスストレス下での安定性への効果を調べるため、パッシベーション膜の形成前後で信頼性評価を行い比較した。バイアスストレスとして、印加電圧はゲートおよびドレインバイアスをそれぞれ 20V とした。室温にて 1, 10, 100, 1000, 10000 秒バイアスストレスを印加した信頼性評価の結果を、図 3-10(a),(b)に示す。

図 3-10(a)に示したパッシベーション膜形成前の ZnO TFT では、バイアスストレスの印加により伝達特性は大きく正側へとシフトし、10000 秒印加後に  $V_{th}$  は約 15Vシフトした。一方で、PA-ALD によりパッシベーション膜を形成した TFT では、この閾値のシフトが大きく改善され、10000 秒印加後の閾値の変化量は約 2V であった。バイアスストレス印加時間に対する  $\Delta V_{th}$  の変化を、図 3-10(c)に示す。

PA-ALD により 100℃という低温で堆積した ZnO およびアルミナ膜を使用した低温プロセス ZnO TFT に対して、同じく PA-ALD により低温形成したアルミナ膜をパッシベーション膜として使用し、特性の向上を試みた。その結果、伝達特性および信頼性の向上に通常必要とされる、高温での熱処理なしでその特性が向上した。このことから、PA-ALD 法を適用することにより、高性能で高い信頼性を有する ZnO TFT の低温での作製が可能となることが明らかとなった。

図 3-10 ゲートおよびドレインバイアスストレス印加による信頼性評価 (a)パッシベーション膜形成前、(b) パッシベーション膜形成後の ZnO TFT のバイアスストレス印加による伝達特性の変化、(c)バイアスストレス下での時間経過による 関値電圧の変化量の推移

## 3.5 PA-ALD による高性能フレキシブル ZnO TFT の作製

#### 3.5.1 PA-ALD による高性能 ZnO TFT の低温作製

本章のこれまでの研究により、ALD により堆積したアルミナ膜をゲート絶縁膜として用いることにより、ZnO TFT の高性能化が可能となることが明らかになった。さらに、第 2 章 7 節に示した ZnO 膜形成時のラジカル源の検討により、PA-ALD でのZnO 膜の堆積時に水をラジカル源として使用する( $H_2O$ -plasma)ことにより、堆積温度を上昇させることなく ZnO TFT の特性の向上が可能となることが分かった。そこで、低抵抗 Si 基板上にゲート絶縁膜として PA- $/O_3$ -ALD による積層アルミナ膜、チャネル層に  $H_2O$ -plasma を使用した PA-ALD により ZnO 膜を堆積し、ZnO TFT を作製した。ZnO 膜はウェットエッチングによりパターニングし、S/D 電極として Ti をリフトオフプロセスで形成した。

作製した TFT に、 $V_d$ =5 V のドレインバイアスを印加し、伝達特性を測定した。 伝達特性および出力特性の測定結果を図 3-11(a)、(b)にそれぞれ示す。PA-ALD により 堆積したアルミナゲート絶縁膜上に、 $O_2$ -plasma により堆積した ZnO 膜を使用した TFT と比較して on 電流が大きく向上し、これにより電界効果移動度の向上がみられた。この時の電界効果移動度の最大値は、約  $10.0~{\rm cm}^2/{\rm Vs}$  であり、 $O_2$ -plasma による ZnO 膜を使用したものと比較しておよそ 2 倍の値を示している。また、 $V_g$  = 0 V でオフ状態のノーマリー・オフの状態が得られ、off 電流は  $10^{-14}$  以下と非常に良好なオフ特性を示した。これにより on/off 比  $10^{10}$  以上、また S 値は約 0.22 V/decade という非常に高いスイッチング特性が得られた。これは、第 2 章 7 節で示した  $H_2$ O-plasma による ZnO 膜の高性能化、および本章 3 節で示した ALD による積層アルミナゲート絶縁膜を使用することによる界面層の形成が効果的に機能した結果であると言える。

図 3-11 低温プロセス ZnO TFT(a)伝達特性、(b)出力特性

#### 3.5.2 フレキシブル基板上 ZnO TFT 作製プロセス

これまでの本研究の結果から、PA-ALD 法による薄膜を用いることで、高性能な ZnO TFT の低温形成が可能となることが明らかとなった。PA-ALD 法による ZnO TFT の作製プロセスの最高温度が  $100^{\circ}$ Cであることから、プラスチックなどのフレキシブル基板上へのデバイスの作製が可能となる。そこで、液晶パネルの輝度向上フィルム、電子部品材料や APS 写真フィルム等にも広く用いられている、ポリエチレンナフタレート( PEN: Polyethylene naphthalate )フィルム上に、高性能な ZnO TFT の作製を試みた。

PEN フィルム (帝人デュポンフィルム株式会社、テオネックス Q65FA) 上に、EB 蒸着により Ti/Al/Au を蒸着し、リフトオフプロセスによりパターニングしてゲート電極を作製した。ゲート電極を形成した PEN 基板上に、PA-ALD 法によりゲート絶縁膜としてアルミナ膜を 50 nm、チャネル層として ZnO 膜をそれぞれ堆積温度 100℃で形成し、フォトリソグラフィ技術を用いてウェットエッチングにより ZnO 膜のパターニングを行った。ソース/ドレイン (S/D) 電極として Ti を用い、リフトオフによりパターニングした後、ウェットエッチングによりゲート電極用コンタクトホールを形成し、図 3-12 に示すようなボトムゲート型 TFT を作製した。

図 3-12 フレキシブル基板上ボトムゲート型 ZnO TFT

#### 3.5.3 フレキシブル ZnO TFT 特性

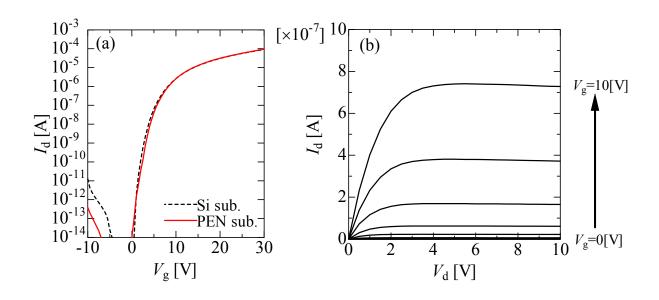

PEN 基板上および比較として Si 基板上に作製した ZnO TFT に、 $V_d = 5$  V を印

加し伝達特性を測定した。測定した伝達特性を図 3-13(a)に、出力特性を図 3-13(b)に示す。フレキシブルな PEN フィルム上に作製した TFT においても、Si 基板上に作製したものと比較して特性の劣化は見られず、良好なスイッチング特性が得られた。

伝達特性では、図 3-13(a)に示す通り、ゲート電圧 0V でドレイン電流が流れない、ノーマリー・オフの状態が得られ、off 電流は  $10^{-14}$  以下と非常に良好なオフ特性を示した。このため、 $10^{10}$  以上という高い on/off 比が得られ、S 値は 0.17 V/decadeと急峻な立ち上がりを示した。さらに、この ZnO TFT の電界効果移動度の最大値は  $17.5~cm^2/Vs$  と、本研究で目的とする次世代ディスプレイの画素駆動素子に求められる、 $10~cm^2/Vs$  以上の電界効果移動度を十分に満たす値が得られた。図 3-13(b)に示した出力特性においても、飽和領域の  $V_d$  において  $I_d$  が増加するキンク電流は見られず、良好な出力特性が得られている。また、特性が  $V_d$  の低い領域で立ち上がっており、これは良好なオーミックコンタクトが得られていることを示している。

図 3-13 フレキシブル基板上 ZnO TFT (a) 伝達特性、(b) 出力特性

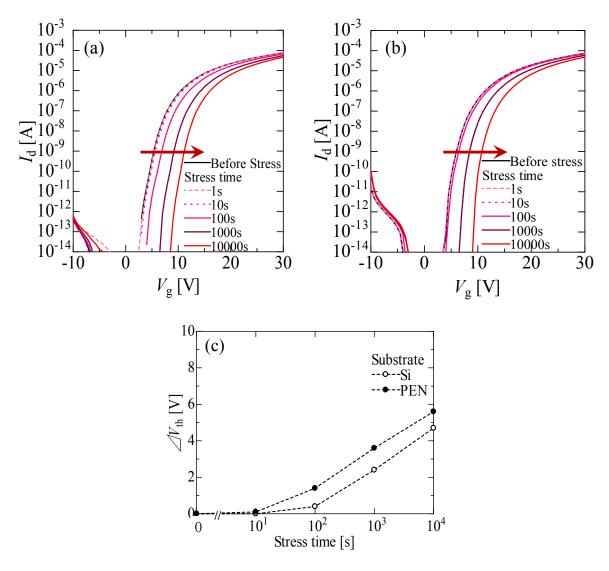

#### **3.5.4** フレキシブル **ZnO TFT** の信頼性評価

フレキシブル基板上に作製した ZnO TFT の、バイアスストレス下における電気的安定性を調べるため、ゲートおよびドレインバイアスを印加し信頼性評価を行った。比較として、Si 基板上に同じ薄膜を堆積し作製した TFT にも同様の測定を行い、フレキシブル基板上に作製したことによる信頼性の変化を確認した。ゲートおよびドレインバイアスストレスとして、それぞれ 10 V 印加した時の信頼性評価の結果を、図 3-14(a),(b)に示す。PEN 基板上、Si 基板上いずれの TFT においても、バイアススト

レスの印加により、時間経過と共に  $V_{th}$  のシフトがみられた。バイアスストレスを 10000 秒印加した時の  $V_{th}$  のシフト量( $\Delta V_{th}$ )は、Si 基板上および PEN 基板上でそれぞれ約 5 V および約 5.5 V と、基板による大きな変化は見られなかった。また、バイアスストレスの印加による S 値の変化は見られなかった。

PA-ALD 法により堆積した ZnO 膜およびアルミナ膜を使用することにより、高性能な ZnO TFT の低温での作製が可能であることを実証した。さらに、フレキシブル基板上においても高い特性を示し、Si 基板上に作製した TFT と同様の特性が得られた。これにより、本研究で目的とする次世代ディスプレイの画素駆動素子として要求される、フレキシブル基板上への作製、高移動度を満たす高性能フレキシブルZnO TFT の作製に成功した。

図 3-14 ゲートおよびドレインバイアスストレス印加による信頼性評価 (a)PEN 基板上、(b) Si 基板上に作製した ZnO TFT のバイアスストレス印加による伝達特性 の変化。(c)バイアスストレス下での時間経過による閾値電圧の変化量の推移

## 3.6 結言

ZnO TFT の特性向上および低温プロセス化に向けて、PA-ALD により堆積した ZnO 膜およびアルミナ膜を使用して ZnO TFT を作製し、その特性を評価した。その結果、ALD により堆積したアルミナ膜を使用することにより、ZnO TFT 特性が大きく向上した。

ZnO 膜を PA-ALD により 300℃で堆積し、ゲート絶縁膜として使用したアルミナ膜の堆積条件の変化による ZnO TFT 特性への影響を調べた。その結果、従来の熱 ALD によるアルミナを使用した TFT( $\mu$ =7.2 cm $^2$ V $^1$ s $^1$ )では、熱酸化膜を使用したもの( $\mu$ =5.7 cm $^2$ V $^1$ s $^1$ )と比較して高い電界効果移動度が得られた。一方で、PA-ALD により堆積したアルミナ膜を使用することにより、TFT の off 電流が低減された。

低温プロセス ZnO TFT の特性向上のため、100℃で堆積した ZnO 膜をチャネ ル層、アルミナ膜をゲート絶縁膜として使用し TFT 特性を調べた。熱 ALD、PA-ALD それぞれによるアルミナ膜の特性を活かし、ZnO TFT のさらなる特性向上を図るため、 熱 ALD/PA-ALD 積層アルミナ膜をゲート絶縁膜として堆積し、その効果を調べた。 その結果、PA-ALDによる単層アルミナ膜をゲート絶縁膜として使用した TFT と比較 して、積層アルミナ膜を使用することにより TFT 特性は大きく向上した。積層アルミ ナ膜をゲート絶縁膜として使用した ZnO TFT において、その電界効果移動度は 5.1  $cm^2V^{-1}s^{-1}$ 、on/off 比は  $> 10^9$  であり、S 値は 0.2 V/decade であった。さらに、バイア スストレス下での安定性も改善された。SIMS 測定による界面付近の測定結果と比較 し、積層アルミナ膜をゲート絶縁膜として使用することによるこれら ZnO TFT の特 性の向上は、ZnO/ゲート絶縁膜界面において界面層が形成されたためであると考えら れる。この界面層には、ZnO だけでなくアルミ原子も含まれていると考えられる。ZnO にアルミをドープした ZnO:Al は導電性を示す透明導電膜材料であり、さらに、ALD による ZnO 膜の堆積において、ZnO 膜数十層に対し1層のアルミナを挟むサンドイ ッチ構造を繰り返すことにより、膜の抵抗率が低減されるという報告がされている。 本研究において ALD による ZnO 堆積時にアルミナ膜の原料である TMA の投入を検 討した結果、TMA を投入することで比抵抗が低減される傾向がみられた。これによ り、ALDで堆積された ZnO 膜は半導体としてだけでなく、透明導電膜としても使用 できることとなり、ZnO膜の更なる高機能化が期待できる。

酸化亜鉛系 TFT において、パッシベーション膜を形成しチャネル層を大気中の水分などから保護することにより、バイアスストレス下での安定性が向上することが知られている。そこで、PA-ALD によるアルミナゲート絶縁膜および ZnO チャネル膜を堆積し作製した低温プロセス ZnO TFT 上に、ALD によりアルミナ膜をパッシベ

ーション膜として形成し、信頼性への効果を調べた。その結果、パッシベーション膜にも PA-ALD 法が有効であることが分かった。さらに、PA-ALD によるアルミナ膜をパッシベーション膜として形成した ZnO TFT では、パッシベーション膜形成前では約 15V であったバイアスストレス印加による 閾値のシフトが、パッシベーション膜形成後は約 2V と大きく改善された。これは、PA-ALD により低温でも高品質な膜の形成が行われたためであると考えられる。

これまでの ZnO TFT の高性能化、低温プロセス化への検討により、薄膜の形成に ALD 法を適用することで作製プロセスの最高温度が  $100^{\circ}$ Cという低温で、高性能な ZnO TFT の作製が可能となった。これは、汎用プラスチック基板等のフレキシブル基板上へのデバイス作製にも十分に対応し得るプロセス温度を示している。そこで、現在液晶パネルや電子部品材料にも使用されている PEN フィルム上に、ZnO TFT の作製を試みた。その結果、電界効果移動度で約  $17.5~{\rm cm}^2{\rm V}^{-1}{\rm s}^{-1}$  という高い値が得られ、本研究で目的とする次世代ディスプレイの画素駆動素子として、十分に対応し得る高性能な ZnO TFT の作製に成功した。

## 参考文献

- 1) R. Puurunen: *J. App. Phys.*, **97** (2005) 121301.

- <sup>2)</sup> N. Blasco: Workshop on 12th International Conference on Atomic Layer Deposition, 2012.

- 3) 服部望, 宮武直正, 村田和俊, 川村悠実, 浦岡行治: *薄膜材料デバイス研究会第6 回研究集会*, 2I01,2009.

- <sup>4)</sup> K. Washio, Y. Mori, n. Miyatake, K. Murata, Y. Sugawara, and Y. Uraoka: *Proc. of IDW'07*, (2007), 549.

- 5) 八百隆文, ZnO 系の最新技術と応用、株式会社 シーエムシー出版 (2007).

- 6) R. Kuse, M. Kundu, T. Yasuda, N. Miyata, and A. Toriumi: *J. Appl. Phys.*, **94** (2003) 6411.

- <sup>7)</sup> I. S. Joen, J. Park, D. Eom, C. S. Hwang, H. J. Kim, C. J. Park, H. Y. Cho, J. H. Lee, and H. K. Kang: *Jpn. J. Appl. Phys.*, **42** (2003) 1222.

- <sup>8)</sup> R. Martins, P. Barquinha, I. Ferreira, L. Pereira, G. Gonçalves and E. Fortunato: *J. Appl. Phys.*, **101**(2007)044505.

- <sup>9)</sup> W. Lim, E. A. Douglas, D. P. Norton, S. J. Pearton, F. Ren, Y.-W. Heo, S. Y. Son and J. H. Yuh: *Appl. Phys. Lett.*, **96**(2010)053510.

- <sup>10)</sup> K. Nomura, T. Kamiya, Y. Kikuchi, M. Hirano, and H. Hosono: *Thin Solid Films*, **518**(2010)3012.

- <sup>11)</sup> K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono: *Nature*, **432** (2004) 488.

- O. K. Varghese, M. Paulose, and C. A. Grimes: *Nat. Nanotechnol.*, **4**(2009)592.

- <sup>13)</sup> M. Law, L. E. Greene, J. C. Johnson, R. Saykally, and P. Yang: *Nat. Mater.*, **4** (2005)455.

- <sup>14)</sup> R. B. H. Tahar, T. Ban, Y. Ohya, and Y. Takahashi: *J. Appl. Phys.*, **82** (1997)865.

- <sup>15)</sup> L. K. Rao, and V. Vinni: *Appl. Phys. Lett.*, **63**(1993) 608.

- <sup>16)</sup> H. Nanto, T. Minami, S. Shooji, and S. Takata: *J. Appl. Phys.*, **55**(1984)1029.

- <sup>17)</sup> T. Minami, H. Sonohara, S. Takata, and H. Sato: *Jpn. J. Appl. Phys.*, **33**(1994) L743.

- <sup>18)</sup> S.-H. K. Park, J.-I. Lee, C.-S. Hwang, and H. Y. Chu: *Jpn. J. Appl. Phys.*, **44**(2005) L242.

- <sup>19)</sup> J. Meyer, P. Görrn, S. Hamwi, H.-H. Johannes, T. Riedl, and W. Kowalsky: *Appl. Phys. Lett.*, **83** (2008) 073308.

- <sup>20)</sup> D.-J. Lee, H.-M. Kim, J.-Y. Kwon, H. Choi, S.-H. Kim, and K.-B. Kim: *Adv. Funct. Mater.*, **21**(2011)448.

- S. I. Kim, C. J. Kim, J. C. Park, I. Song, S. W. Kim, H. Yin, E. Lee, J. C. Lee, and Y. Park: *IEEE International Electron Device Meeting*, (2008).

- <sup>22)</sup> W. Kim, S.-H. Lee, J.-H. Bang, H.-S. Uhm, and J.-S. Park: *Thin Sold Films*, **520** (2011) 1475.

- <sup>23)</sup> J. S. Park, J. K. Jeong, H. J. Chung, Y. G. Mo, and H. D. Kim: *Appl. Phys. Lett.*, **92** (2008) 072104.

- <sup>24)</sup> P. -T. Liu, Y. -T. Chou, and L. -F. Teng: *Appl. Phys. Lett.*, **95** (2009) 233504

- <sup>25)</sup> C. Tu, W. Lin, C. Chen, M. Hung, J. Chang, and M. Chiang: *SID Symposium Digest of Technical Papers*, **42** (2011) 1151.

- <sup>26)</sup> J.S. Park, T.S.Kim, K.S. Son, K.H. Lee, W.J. Maeng, and H.S. Kim: *Appl. Phys. Lett.*, **96** (2010) 2621091.

# 第4章 非晶質 In-Ga-Zn-O TFT 特性における ALD 絶縁膜の効果